## UNIVERSIDADE FEDERAL DO RIO GRANDE CENTRO DE CIÊNCIAS COMPUTACIONAIS PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO MESTRADO EM ENGENHARIA DE COMPUTAÇÃO

Dissertação de Mestrado

## Análise dos métodos PTM e SPR para a avaliação de confiabilidade de circuitos combinacionais

Matheus Ferreira Pontes

Dissertação de Mestrado apresentada ao Programa de Pós-Graduação em Computação da Universidade Federal do Rio Grande, como requisito parcial para a obtenção do grau de Mestre em Engenharia de Computação

Orientador: Prof. Dr. Denis Teixeira Franco Co-orientador: Prof. Dr. Paulo Francisco Butzen

#### Ficha catalográfica

P814a Pontes, Matheus Ferreira.

Análise dos métodos PTM e SPR para a avaliação de confiabilidade de circuitos combinacionais / Matheus Ferreira Pontes. – 2019.

99 f.

Dissertação (mestrado) – Universidade Federal do Rio Grande – FURG, Programa de Pós-Graduação em Computação, Rio Grande/RS, 2019.

Orientador: Dr. Denis Teixeira Franco. Coorientador: Dr. Paulo Francisco Butzen.

1. Circuitos Digitais 2. Confiabilidade 3. PTM 4. SPR 5. SPR-MP I. Franco, Denis Teixeira II. Butzen, Paulo Francisco III. Título.

CDU 004.312.2

Catalogação na Fonte: Bibliotecário José Paulo dos Santos CRB 10/2344

# MINISTÉRIO DA EDUCAÇÃO UNIVERSIDADE FEDERAL DO RIO GRANDE CENTRO DE CIÊNCIAS COMPUTACIONAIS PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO CURSO DE MESTRADO EM ENGENHARIA DE COMPUTAÇÃO

## ATA DE SESSÃO DE DEFESA DE DISSERTAÇÃO DE MESTRADO

Ata nº <u>01</u>/201<u>9</u>

Na data de 06 de março de 2019, às 14 horas, ocorreu a Sessão de Defesa de Dissertação de Mestrado de Matheus Ferreira Pontes, que apresentou a dissertação intitulada Análise Dos Métodos PTM e SPR para Avaliação de Confiabilidade de Circuitos Combinacionais, realizada sob a orientação do Prof. Dr. Denis Teixeira Franco e coorientação do Prof. Dr. Paulo Francisco Butzen. A banca examinadora foi constituída pela Profa. Dra. Cristina Meinhardt (UFSC) e pelo Prof. Leomar Soares da Rosa Jr. (UFPEL), sob a presidência do orientador. Após a apresentação do trabalho, a banca arguiu o candidato e, a seguir, deliberou pela

| (≥ | 🔾 aprovação da Dissertação  |                                 |

|----|-----------------------------|---------------------------------|

| (  | ) aprovação da Dissertação, | sugerindo modificações no texto |

| (  | ) reprovação da Dissertação |                                 |

Rio Grande, 06 de março de 2019

Profa. Dra. Éristina Meinhardt

Prof. Dr. Leomar Soares da Rosa Jr.

Prof. Dr. Denis Teixeira Franco

enis V. Dance

Orientador

Prof. Dr. Paulo Francisco Butzen

Corientador

## **AGRADECIMENTOS**

Agradeço a minha família pelo apoio incondicional na minha caminhada acadêmica. Agradeço também aos meus orientadores pela paciência e compreensão em vários momentos.

#### **RESUMO**

PONTES, Matheus Ferreira. **Análise dos métodos PTM e SPR para a avaliação de confiabilidade de circuitos combinacionais**. 2019. 99 f. Dissertação (Mestrado) – Programa de Pós-Graduação em Computação. Universidade Federal do Rio Grande, Rio Grande.

A confiabilidade de um circuito é uma informação importante principalmente quando o mesmo é projetado em tecnologias nanométricas. Este trabalho traz implementações de três métodos que estimam a confiabilidade de circuitos digitais: Matrizes de Transferência Probabilística (PTM), Análise de Confiabilidade pela Probabilidade de Sinais (SPR) e uma variação do SPR denominada SPR-Multipass (SPR-MP). São exploradas as vantagens e desvantagens de cada um, visando a aplicabilidade no processo de projeto de circuitos. A PTM já foi amplamente discutida na literatura, sendo considerada uma metodologia exata para estimar a confiabilidade de um circuito, apresentando, entretanto, restrições de escalabilidade. No presente trabalho, foi desenvolvida uma implementação alternativa, que sequencializa os cálculos envolvendo matrizes. Outro método que será abordado é o SPR, o qual não possui problemas com escalabilidade, pois sua complexidade é linear em relação ao número de portas. Porém, por não tratar os fanouts reconvergentes, os valores de confiabilidade encontrados com o SPR não são precisos. O SPR-MP é uma variação do SPR focada em lidar com a reconvergência de sinais e estimar a confiabilidade de um circuito de forma exata. O tempo de processamento do SPR-MP está diretamente relacionado à quantidade de fanouts do circuito, o que também pode inviabilizar a utilização do método para circuitos maiores. Assim, neste trabalho foram realizadas comparações entre os métodos, a fim de verificar as vantagens e desvantagens de cada um. O método PTM se mostrou impraticável para estimar a confiabilidade de circuitos com mais de duas dezenas de portas. Tendo em vista que o SPR-MP também gera resultados exatos de confiabilidade, quando todos os fanouts são considerados, a amostragem de circuitos pôde ser ampliada em termos de tamanho de circuito. Realizando comparações entre os métodos SPR e SPR-MP foi possível identificar certas tendências nos resultados obtidos pelo método SPR. Em termos numéricos, a diferença entre os valores de confiabilidade gerados pelo SPR e o valor exato é na sua grande maioria menor que 10%. Além disso, a redução no tempo de processamento, quando usado o SPR, pode chegar até 108 vezes o tempo necessário para extrair um valor exato. Estas características fazem com que o SPR seja uma excelente alternativa para uma rápida estimativa da confiabilidade de um circuito.

Palavras-chave: Circuitos Digitais, Confiabilidade, PTM, SPR, SPR-MP.

#### **ABSTRACT**

PONTES, Matheus Ferreira. Combinational Circuit Reliability Analysis Using PTM and SPR. 2019. 99 f. Dissertação (Mestrado) – Programa de Pós-Graduação em Computação. Universidade Federal do Rio Grande, Rio Grande.

The reliability of a circuit is an important information mainly when it is designed in nanometric technologies. This work presents implementations of three methods that estimate the reliability of digital circuits: Probabilistic Transfer Matrices (PTM), Signal Probability Reliability Analysis (SPR) and a SPR variation called SPR-Multipass (SPR-MP). The advantages and disadvantages of each one will be explored, aiming at the applicability in the circuit design process. PTM has already been widely discussed in the literature, being considered an exact methodology to estimate the reliability of a circuit, presenting, however, scalability constraints. In the present work, an alternative implementation was developed that sequentially calculates matrices. Another method that will be presented is the SPR, which has no problems with scalability, because its complexity is linear in relation to the number of gates. However, since it does not handle reconvergent fanouts, the encountered reliabilities values with the SPR are not accurate. The SPR-MP is a variation of the SPR focused on dealing with the reconvergence of signals and accurately estimating the reliability of a circuit. The processing time of the SPR-MP is directly related to the amount of fanouts of the circuit, which may also make it unfeasible to use the method for larger circuits. Thus, in this work comparisons were made between the methods to verify the advantages and disadvantages of each one. The PTM method is impractical to estimate the reliability of circuits with more than two dozen ports. Since SPR-MP also generates accurate reliability results, when all fanouts are considered, circuit sampling could be expanded in terms of size. By making comparisons between the SPR and SPR-MP methods it was possible to identify certain trends in the results obtained by the SPR method. In numerical terms, the difference between the reliability values generated by the SPR and the exact value is, for the most part, less than 10 %. In addition, the reduction in processing time, when used the SPR, can reach up to  $10^8$  times the time needed to extract an exact value. These characteristics make the SPR an excellent alternative for a rapid estimation of the reliability of a circuit.

Keywords: Digital Circuits, Reliability, PTM, SPR, SPR-MP.

## **LISTA DE FIGURAS**

| Figura 1<br>Figura 2                                                                                                           | Taxonomia de confiabilidade                                                                                                                                                                                                                                                                                               |                                                          |  |

|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|

| Figura 3                                                                                                                       | Diagrama da Curva da Banheira                                                                                                                                                                                                                                                                                             | 19                                                       |  |

| Figura 4 Figura 5 Figura 6 Figura 7 Figura 8 Figura 9 Figura 10 Figura 11                                                      | Exemplos de arranjos de fios condutores                                                                                                                                                                                                                                                                                   | 24<br>24<br>26<br>27<br>28<br>29<br>30<br>31             |  |

| Figura 12<br>Figura 13<br>Figura 14<br>Figura 15<br>Figura 16<br>Figura 17<br>Figura 18<br>Figura 19<br>Figura 20<br>Figura 21 | Diagrama de classes da estrutura especializada  Ferramenta desenvolvida  Pseudo-código da PTM tradicional  Demonstração do Tensor de Kronecker  Processo Inverso da Aplicação do Tensor de Kronecker  Formação do elemento 5 × 4 da matriz resultante  Formação da Matriz PTM de um Circuito  Pseudo-código do Método SPR | 32<br>33<br>34<br>37<br>38<br>38<br>39<br>40<br>41<br>42 |  |

| Figura 22<br>Figura 23<br>Figura 24                                                                                            | Percentual de incremento no MTBF do circuito, melhores casos                                                                                                                                                                                                                                                              | 51<br>60<br>60                                           |  |

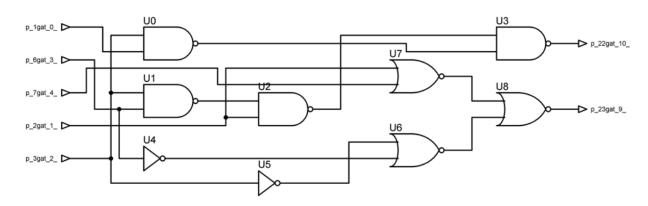

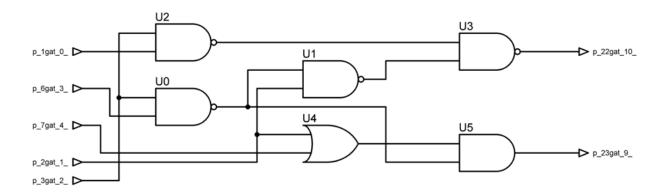

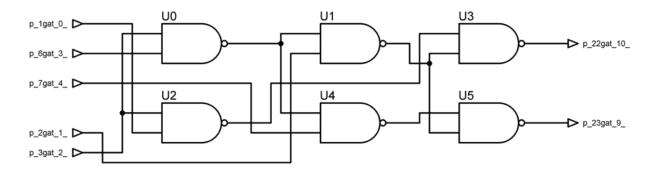

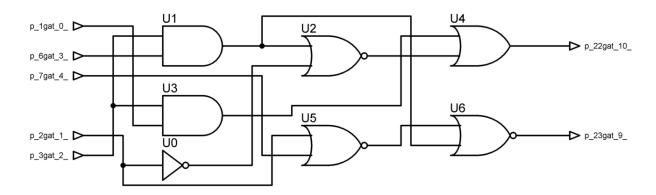

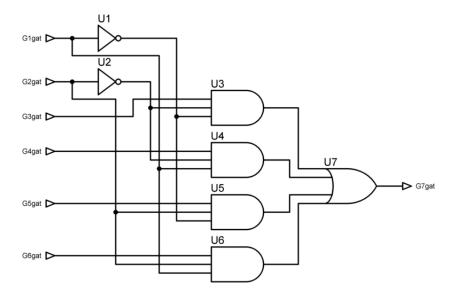

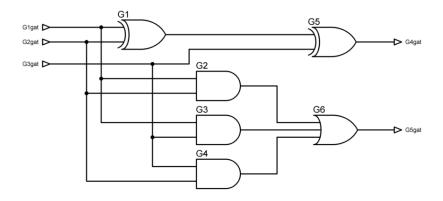

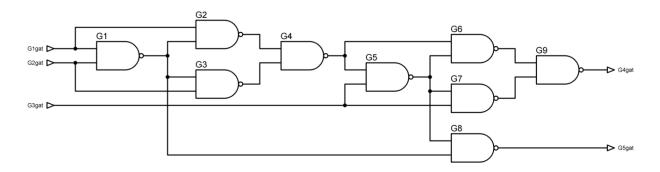

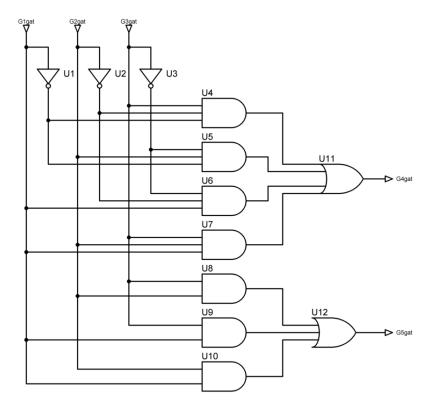

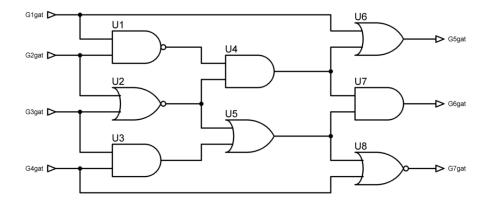

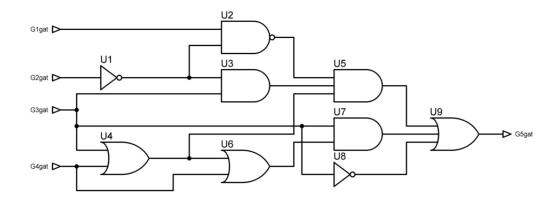

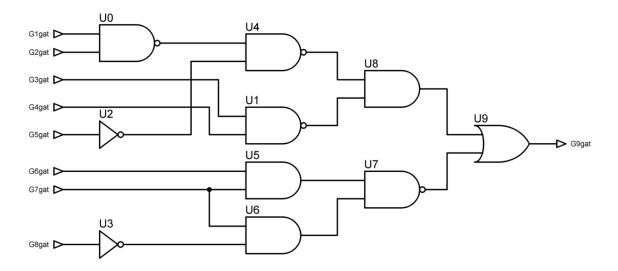

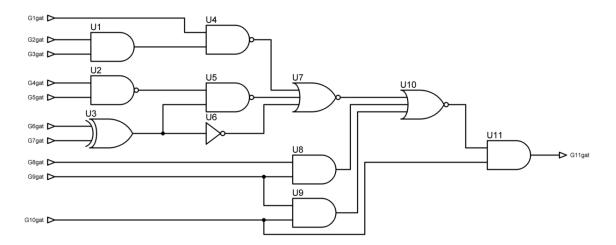

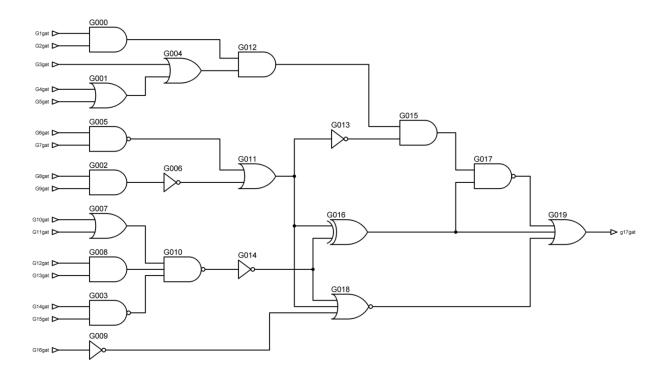

| Figura 25 Figura 26 Figura 27 Figura 28 Figura 29 Figura 30 Figura 31 Figura 32                                                | C17 - Versão 2 C17 - Versão 3 C17 - Versão 4 Multiplexador 4-bits Somador Completo - Versão 1 Somador Completo - Versão 2                                                                                                                                                                                                 | 67<br>68<br>68<br>68<br>69<br>69                         |  |

| Figura 33                                                                                                                      |                                                                                                                                                                                                                                                                                                                           | 70                                                       |  |

| Figura 34 | C9                                  |

|-----------|-------------------------------------|

| Figura 35 | C10                                 |

| Figura 36 | C11                                 |

| Figura 37 | C20                                 |

| Figura 38 | Descrição do s27                    |

| Figura 39 | Descrição do s208                   |

| Figura 40 | Descrição do s298 (saída n64)       |

| Figura 41 | Descrição do s344 (saída n61)       |

| Figura 42 | Descrição do s349 (saída n66)       |

| Figura 43 | Descrição do s382 (saída n69)       |

| Figura 44 | Descrição do s386 (saída n49)       |

| Figura 45 | Descrição do s400 (saída n64)       |

| Figura 46 | Descrição do s420 (saída Z)         |

| Figura 47 | Descrição do s444 (saída n109)      |

| Figura 48 | Descrição do s510 (saída n78)       |

| Figura 49 | Descrição do s641 (saída n178)      |

| Figura 50 | Descrição do s713 (saída n177)      |

| Figura 51 | Descrição do s820 (saída n95)       |

| Figura 52 | Descrição do s832 (saída n90)       |

| Figura 53 | Descrição do s838 (saída n215)      |

| Figura 54 | Descrição do s953 (saída n104)      |

| Figura 55 | Descrição do s1196 (saída G542)     |

| Figura 56 | Descrição do s1238 (saída n117)     |

| Figura 57 | Descrição do s1423 (saída n90)      |

| Figura 58 | Descrição do s1488 (saída n75)      |

| Figura 59 | Descrição do s1494 (saída n70)      |

| Figura 60 | Descrição do s5378 (saída n240)     |

| Figura 61 | Descrição do s9234 (saída n676)     |

| Figura 62 | Descrição do s13207 (saída n594) 91 |

| Figura 63 | Descrição do s15850 (saída n460)    |

| Figura 64 | Descrição do s38417 (saída n7962)   |

| Figura 65 | Descrição do s38584 (saída n7656)   |

|           |                                     |

## LISTA DE TABELAS

| Tabela 1  | Memória estimada para armazenar as maiores matrizes             | 44 |

|-----------|-----------------------------------------------------------------|----|

| Tabela 2  | Apresentação dos circuitos que serão utilizados nas comparações | 45 |

| Tabela 3  | Comparação entre PTM e PTM Serial                               | 46 |

| Tabela 4  | Aplicação do método SPR sobre os ISCAS85                        | 47 |

| Tabela 5  | Comparação entre as confiabilidades obtidas pela PTM e SPR      | 48 |

| Tabela 6  | Comparação entre PTM e SPR-MP                                   | 49 |

| Tabela 7  | Comparação entre PTM Serial e SPR-MP                            | 49 |

| Tabela 8  | ISCAS89 versão combinacional                                    | 52 |

| Tabela 9  | Nova amostragem de circuitos                                    | 53 |

| Tabela 10 | Apresentação de valores de confibilidade em MTBF                | 54 |

| Tabela 11 | Diferença Percentual entre diferentes números de fanouts        | 54 |

| Tabela 12 | Diferenças Percentuais entre os tempos de processamento         | 55 |

| Tabela 13 | Diferenças entre SPR-MP e SPR                                   | 56 |

| Tabela 14 | Classificação dos circuitos mais confiáveis                     | 57 |

| Tabela 15 | Portas que mais afetam a confiabilidade do s444                 | 58 |

| Tabela 16 | Diferença percentual entre os valores e o valor de MTBF         | 59 |

| Tabela 17 | Análise SPR-MP: Quantidade de fanouts analisados                | 96 |

| Tabela 18 | Análise SPR-MP: diferentes quantidades de fanouts               | 97 |

| Tabela 19 | Análise SPR-MP: Diferenças percentuais                          | 98 |

| Tabela 20 | Análise SPR-MP: Tempos de processamento(ms)                     | 99 |

| Tabela 21 | Análise SPR-MP: Tempos de processamento                         | 99 |

#### LISTA DE ABREVIATURAS E SIGLAS

BC Bathtube Curve

BN Bayesian Network

CI Circuito Integrado

CTMC Continuous-time Markov Chains

DTMC Discrete time Markov Chains

ESD Electrostatic discharge

FIT Failure in Time

ISCAS International Symposium on Circuits and Systems

ITM Ideal Transfer Matrix

MTBF Meantime Between Failure

PGM Probabilistic Gate Model

PMC Probabilistic Model Check

PRISM Probabilistic Symbolic Model Checker

PTM Probabilistic Transfer Matrix(ces)

SET Single-Event Transient

SPR Signal Probability Reliability

SPR-MP Signal Probability Reliability - Multi Pass

## **SUMÁRIO**

| 1 II                                                                           | NTRODUÇÃO                                                                                                                                                                                                                           | 12                                                             |

|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 1.1                                                                            | Falhas em Circuitos Digitais                                                                                                                                                                                                        | 13                                                             |

| 1.2                                                                            | Mascaramento                                                                                                                                                                                                                        | 14                                                             |

| 1.2.1                                                                          | Mascaramento Elétrico                                                                                                                                                                                                               | 14                                                             |

| 1.2.2                                                                          | Mascaramento Temporal                                                                                                                                                                                                               | 15                                                             |

| 1.2.3                                                                          | Mascaramento Lógico                                                                                                                                                                                                                 | 15                                                             |

| 1.3                                                                            | Objetivos                                                                                                                                                                                                                           | 15                                                             |

| 1.4                                                                            | Organização do Trabalho                                                                                                                                                                                                             | 17                                                             |

|                                                                                | CONCEITOS E MÉTODOS EM ANÁLISE DE CONFIABILIDADE                                                                                                                                                                                    | 18                                                             |

| 2.1                                                                            | Definições e Métricas                                                                                                                                                                                                               | 18                                                             |

| 2.2                                                                            | Simulação e Injeção Física de Falhas                                                                                                                                                                                                | 20                                                             |

| 2.3                                                                            | Simulação de Monte Carlo                                                                                                                                                                                                            | 20                                                             |

| 2.4                                                                            | Abordagens Analíticas                                                                                                                                                                                                               | 21                                                             |

| 3 (                                                                            | OS MÉTODOS PTM E SPR                                                                                                                                                                                                                | 23                                                             |

| 3.1                                                                            | Matriz de Transferência Probabilística                                                                                                                                                                                              | 23                                                             |

| 3.2                                                                            | Confiabilidade pela Probabilidade de Sinais                                                                                                                                                                                         | 27                                                             |

| 3.2.1                                                                          | SPR Multi-Pass                                                                                                                                                                                                                      | 30                                                             |

|                                                                                |                                                                                                                                                                                                                                     |                                                                |

| 4 F                                                                            | ERRAMENTA DESENVOLVIDA                                                                                                                                                                                                              | 32                                                             |

| 4 F<br>4.1                                                                     | FERRAMENTA DESENVOLVIDA                                                                                                                                                                                                             | 32<br>32                                                       |

|                                                                                |                                                                                                                                                                                                                                     |                                                                |

| 4.1                                                                            | Descrição da Ferramenta                                                                                                                                                                                                             | 32                                                             |

| <b>4.1</b> 4.1.1                                                               | Descrição da Ferramenta                                                                                                                                                                                                             | 32<br>35                                                       |

| <b>4.1</b> 4.1.1 4.1.2 4.1.3                                                   | Descrição da Ferramenta                                                                                                                                                                                                             | 32<br>35<br>40                                                 |

| <b>4.1</b> 4.1.1 4.1.2 4.1.3                                                   | Descrição da Ferramenta  PTM                                                                                                                                                                                                        | 32<br>35<br>40<br>41                                           |

| <b>4.1</b> 4.1.1 4.1.2 4.1.3                                                   | Descrição da Ferramenta  PTM                                                                                                                                                                                                        | 32<br>35<br>40<br>41<br>43                                     |

| 4.1<br>4.1.1<br>4.1.2<br>4.1.3<br>5 F<br>5.1                                   | Descrição da Ferramenta  PTM                                                                                                                                                                                                        | 32<br>35<br>40<br>41<br>43<br>43                               |

| <b>4.1</b> 4.1.1 4.1.2 4.1.3 <b>5 F 5.1</b> 5.1.1                              | Descrição da Ferramenta  PTM  SPR  SPR  SPR-MP  RESULTADOS  Comparações entre os métodos  PTM e PTM-Serial                                                                                                                          | 32<br>35<br>40<br>41<br>43<br>43<br>44                         |

| <b>4.1</b> 4.1.1 4.1.2 4.1.3 <b>5 F 5.1</b> 5.1.1                              | Descrição da Ferramenta  PTM                                                                                                                                                                                                        | 32<br>35<br>40<br>41<br>43<br>43<br>44<br>46                   |

| <b>4.1</b> 4.1.1 4.1.2 4.1.3 <b>5 F 5.1</b> 5.1.1 5.1.2 5.1.3                  | Descrição da Ferramenta  PTM  SPR  SPR  SPR-MP  RESULTADOS  Comparações entre os métodos  PTM e PTM-Serial  SPR  PTM e SPR  PTM e SPR  PTM e SPR-MP  PTM-Serial e SPR-MP                                                            | 32<br>35<br>40<br>41<br>43<br>43<br>44<br>46<br>47             |

| <b>4.1</b> 4.1.2 4.1.3 <b>5 F 5.1</b> 5.1.2 5.1.3 5.1.4                        | Descrição da Ferramenta PTM                                                                                                                                                                                                         | 32<br>35<br>40<br>41<br>43<br>43<br>44<br>46<br>47<br>48       |

| <b>4.1</b> 4.1.1 4.1.2 4.1.3 <b>5 F 5.1</b> 5.1.2 5.1.3 5.1.4 5.1.5            | Descrição da Ferramenta PTM . SPR . SPR-MP .  RESULTADOS .  Comparações entre os métodos PTM e PTM-Serial . SPR . PTM e SPR . PTM e SPR . PTM e SPR-MP . PTM-Serial e SPR-MP . PTM-Serial e SPR-MP . Nova amostragem de circuitos . | 32<br>35<br>40<br>41<br>43<br>43<br>44<br>46<br>47<br>48<br>48 |

| <b>4.1</b> 4.1.2 4.1.3 <b>5 F 5.1</b> 5.1.1 5.1.2 5.1.3 5.1.4 5.1.5 <b>5.2</b> | Descrição da Ferramenta PTM SPR SPR-MP  RESULTADOS Comparações entre os métodos PTM e PTM-Serial SPR PTM e SPR PTM e SPR PTM e SPR-MP PTM-Serial e SPR-MP Expandindo as análises com o SPR-MP                                       | 32<br>35<br>40<br>41<br>43<br>44<br>46<br>47<br>48<br>50       |

| REFERÊNCIAS | 3                                                     | 63 |

|-------------|-------------------------------------------------------|----|

| APÊNDICE A  | AMOSTRA DE CIRCUITOS DA PRIMEIRA ANÁLISE              | 67 |

| APÊNDICE B  | DESCRIÇÃO VERILOG DOS CIRCUITOS DA SEGUNDA AMOSTRAGEM | 72 |

| APÊNDICE C  | ANÁLISE FANOUTS SPR-MP                                | 95 |

## 1 INTRODUÇÃO

Equipamentos eletrônicos estão onipresentes no cotidiano das pessoas, desde o uso para entretenimento ao auxílio em processos industriais. Tais dispositivos são formados por sistemas digitais integrados ou circuitos integrados (CI) (BUTZEN, 2012). A evolução dos circuitos integrados levou-os a escalas nanométricas nos dias atuais, de acordo com a premissa da "Lei de Moore", que diz que a cada 2 anos a densidade dos transistores dobra (MOORE, 1965). Grande parte dos circuitos integrados são projetados usando um fluxo automático auxiliado por computadores, onde diversos algoritmos de síntese são utilizados para gerar o leiaute circuito a ser fabricado. O bloco básico deste fluxo são as portas lógicas e estas por sua vez, são compostas por arranjos de transistores (KRAVETS, 2001).

A concepção do transistor foi responsável pela revolução da microeletrônica e, consequentemente, da computação no último século. Esse dispositivo funciona de forma simplificada como uma chave "liga-desliga", a qual implementa a linguagem binária dos computadores. Com transistores cada vez menores, os circuitos integrados passam a comportar uma grande quantidade desses dispositivos por área, o que possibilita um incremento nas funcionalidades dos sistemas. Nesta mesma linha, aspectos como velocidade e consumo de energia também são melhorados quando se entra na escala nanométrica da construção de circuitos. Entretanto, quanto menores são os transistores, maiores são as vulnerabilidades envolvidas (XIAO et al., 2017). Isso faz com que aumentem as chances de ocorrerem falhas ainda no processo de fabricação, falhas transitórias durante a utilização do circuito e também falhas por envelhecimento com o passar do tempo de utilização do sistema (CHOUDHURY; MOHANRAM, 2007).

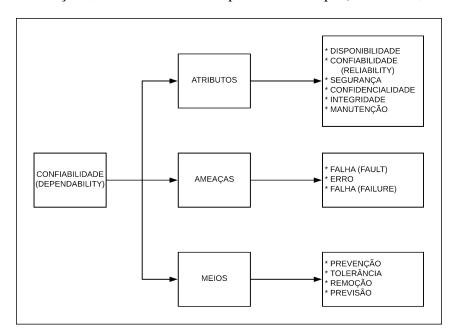

Assim surge o termo "confiabilidade" que pode ser inserido em diversos escopos, pois não se restringe apenas à Ciência da Computação. No contexto deste trabalho, o conceito se insere dentro de uma das quatro propriedades fundamentais de sistemas eletrônicos: confiabilidade, funcionalidade, desempenho e custo (AVIZIENIS et al., 2001). Contudo, a tradução do termo para o português pode gerar ambiguidades, visto que em tradução direta, "dependability" equivale a confiabilidade, bem como "reliability" também equivale a confiabilidade. A ambiguidade pode ser visualizada na taxonomia do termo, demonstrado

na Fig. 1. Assim, a confiabilidade relacionada a "dependability" é uma característica mais ampla de um sistema, aquela que garante o correto funcionamento, ou seja, pode ser definido como a habilidade de um produto ou sistema de funcionar, dentro dos padrões e limites estabelecidos (KAPUR; PECHT, 2014). Já a confiabilidade oriunda de "reliability", é definida como a probabilidade de um sistema executar uma determinada função, sobre certas condições, em um determinado período de tempo (BIROLINI, 2012).

Figura 1: Taxonomia de confiabilidade adaptado de (AVIZIENIS et al., 2004)

#### 1.1 Falhas em Circuitos Digitais

A miniaturização dos circuitos digitais possibilitou grandes avanços na indústria de semicondutores em termos de desempenho. Grande parte deste desempenho está relacionado com o tamanho e a baixa tensão dos transistores. Contudo, a mesma tecnologia que aumenta o desempenho dos arranjos de transistores, os torna menos confiáveis e mais sensíveis a falhas. Tendo em vista que todos os elementos padrões de um circuito digital são formados por redes de transistores, a confiabilidade de um transistor impacta diretamente a confiabilidade de todo o circuito. As falhas que afetam um circuito digital são destacadas conforme a sua fonte e duração e, segundo (MISKOV-ZIVANOV; MARCU-LESCU, 2006) podem ser classificadas em 3 tipos:

- **falhas permanentes** são aquelas que afetam de forma definitiva as característica de um circuito, e que permanecem ativas até que um reparo seja feito (ex: *stuck-at-zero* e *stuck-at-one*);

- falhas transientes (soft ou single-event upset) são aquelas que ocorrem em um curto espaço de tempo e desaparecem, mas que podem causar uma mudança no

estado do circuito, sendo geralmente causadas por fenômenos físicos externos, tais como choques de partículas alpha e nêutrons, Descarga Eletrostática (ESD), dentre outros; e

• falhas intermitentes são aquelas que causam um comportamento errático no circuito em intervalos não padronizados, e que após a primeira ocorrência são grandes a chances de se tornar uma falha permanente.

#### 1.2 Mascaramento

As propriedades de mascaramento dos circuitos digitais podem influenciar na percepção da confiabilidade final do circuito (PAGLIARINI, 2013). Tal característica se deve ao fato de que vários problemas em circuitos não são percebidos pois são "mascarados". Assim serão abordados neste trabalho três dos principais tipos de mascaramento.

Figura 2: Efeito dos mascaramentos Elétrico, Temporal e Lógico causados por um choque de partícula (RAMANARAYANAN et al., 2009)

#### 1.2.1 Mascaramento Elétrico

O mascaramento elétrico pode ser caracterizado pela capacidade de um circuito combinacional atenuar o efeito de um pulso elétrico, gerado por um choque de uma partícula com uma porta lógica, através das portas lógicas subsequentes (GEORGE; LACH, 2011). Como pode ser observado na Fig. 2, uma porta NAND2 foi atingida por uma partícula. Por conseguinte, o valor errado é propagado até a saída do circuito. Contudo, o pulso foi atenuado ao passar pelas portas subsequentes. Neste exemplo foi utilizado uma porta NAND2, mas o efeito pode ser observado em outros tipos de portas lógicas. A explicação

para o efeito se deve à composição de dois efeitos elétricos que reduzem a força do pulso, conforme este passa pelas portas lógicas. O atraso ou *delay* do circuito causado pelo tempo de troca dos transistor aumenta o tempo de subida e queda do pulso. Além disso, existe o fato de que a amplitude de um pulso em curto espaço de tempo, tende a cair, devido ao desligamento da porta antes de atingir toda a amplitude do pulso. Estes dois efeitos somados causam uma redução na duração do pulso e da amplitude, fazendo com que diminuam as chances de uma propagação ocorrer.

#### 1.2.2 Mascaramento Temporal

Este tipo de mascaramento é observado quando uma falha é propagada até a saída de um circuito, gerando um valor inapropriado. Porém, se o momento de manifestação de tal falha está fora do ciclo de gravação de uma célula de memória ligada a saída deste circuito, a falha será mascarada, pois não será armazenada (KRISHNASWAMY; MARKOV; HAYES, 2008). Na Fig. 2, mais precisamente no lado superior direto, está representado o efeito do mascaramento temporal. É preciso destacar que a miniaturização dos circuitos propicia que maiores frequências sejam utilizadas, assim cada vez menos se pode contar com os efeitos do mascaramento temporal.

#### 1.2.3 Mascaramento Lógico

O mascaramento lógico depende exclusivamente da topologia do circuito e não é afetado pela miniaturização da tecnologia (FRANCO, 2008). Assim, os dois tipos de mascaramentos anteriores irão se manifestar apenas se a falha não for mascarada logicamente. O efeito do mascaramento lógico, também é demonstrado na Fig. 2. A saída da NAND2 atingida por um partícula é um *fanout*, a qual é o sinal de entrada de outras duas portas NAND2. Observando de cima para abaixo, a segunda porta NAND2 recebe o valor errado "1". Contudo, independente do valor ser errado ou não, o valor do sinal de entrada **I5** é "0", o que determina o valor correto da saída desta porta lógica. Este trabalho irá explorar as propriedades do mascaramento lógico em circuitos combinacionais para estimar a confiabilidade.

#### 1.3 Objetivos

A estimativa de confiabilidade é de suma importância para o desenvolvimento de circuitos mais robustos. Diversos métodos que estimam a confiabilidade de circuitos foram propostos. A partir da literatura correlata, pode ser inferido que métodos exatos exigem um alto poder computacional para obter resultados. Além disso, dependendo do tamanho do circuito, o processo de estimativa se torna inviável. O método PTM é um exemplo clássico desta característica, onde é possível lidar e obter a confiabilidade de circuitos pequenos. Porém, quando é necessário o tratamento de circuitos com mais de duas deze-

nas de portas, o método se torna impraticável. Contudo, a exatidão do método o faz ser uma base de comparação no desenvolvimento de novos métodos. Nesse contexto, surge o método Confiabilidade pela Probabilidade de Sinais - SPR, sendo uma alternativa para a estimativa de circuitos baseado nas probabilidades de sinais. O SPR tem complexidade linear ao número de portas do circuito, caracterizando-o como um método sem problema de escalabilidade. Por outro lado, na presença de fanouts reconvergentes, o método considera o mesmo sinal, no mesmo instante, com valores distintos, ou seja, ele propaga valores errados, ocasionando um resultado de confiabilidade não exato. Assim, foi proposta uma variação deste método, denominada SPR Multi-pass (SPR-MP), a qual busca, além de lidar com o problema de fanouts, a precisão do resultado a ser obtido. Mais uma vez é demonstrado que a exatidão sempre tem um custo computacional elevado, e no caso do SPR-MP, é necessário percorrer diversas vezes o mesmo circuito, onde o número total de ciclos irá depender tanto do número de fanouts, quanto da posição onde estes estão localizados no circuito. Em relação à PTM, o SPR-MP é uma opção que não demanda grande quantidade de memória para estimar confiabilidade. Por outro lado, o tempo de processamento em circuitos grandes, considerando todos os fanouts, torna o SPR-MP tão impraticável quanto o método PTM.

Assim sendo, este trabalho tem como proposta explorar os métodos PTM, SPR e SPR-MP, no intuito de estabelecer seus limites de análise de confiabilidade. Para atingir este objetivo, é necessário entender e comparar os três métodos, verificando suas vantagens e desvantagens com relação aos custos de memória e de processamento. Os métodos PTM e SPR-MP geram resultados exatos de confiabilidade, o que os torna métodos equivalentes, tanto com relação à precisão dos resultados, quanto com relação aos problemas de escalabilidade. O problema de armazenamento do método PTM já foi amplamente explorado na bibliografia. Contudo, formas de trabalhar de forma sequencial com os cálculos da PTM, podem ser uma alternativa para ampliar a utilização deste método clássico. Essa alternativa também será explorada neste trabalho. Sobre o SPR-MP, considerar a totalidade das combinações entre os fanouts reconvergentes, o torna um método exato, porém impraticável dependendo do número de fanouts. Por outro lado, o método propõe alternativas para diminuir o número total de ciclos, ao custo da precisão do valor de confiabilidade a ser obtido. Além disso, cada fanout contribui de forma distinta na confiabilidade de todo o circuito. Esta característica também pode ser investigada, a fim de tornar seu uso viável. Por fim, levando em conta os três métodos, o SPR é o único que possui complexidade linear, o que possibilita a utilização em circuitos maiores que os outros dois métodos. Mesmo gerando valores de confiabilidade não exatos, é possível avaliar se o SPR pode se tornar uma métrica na estimativa de confiabilidade em circuitos digitais.

#### 1.4 Organização do Trabalho

As próximas seções são organizadas como segue. A Seção II trará uma visão geral dos modelos de análise de confiabilidade existentes. A Seção III será dedicada à parte teórica dos modelos PTM, SPR e SPR-MP. Na Seção IV será descrita a forma como foi implementada e desenvolvida a ferramenta. Já na Seção V são demonstrados os resultados obtidos com as implementações dos três métodos, utilizando tanto os circuitos do *benchmark* ISCAS85 (BRGLEZ; FUJIWARA, 1985), quanto uma amostragem de circuitos menores. Por fim, na Seção VI as conclusões do trabalho são apresentadas.

## 2 CONCEITOS E MÉTODOS EM ANÁLISE DE CONFIA-BILIDADE

O incremento na complexidade dos circuitos integrados, diretamente relacionado com escalas nanométricas, exige que seja possível analisar, antes de sua fabricação, o seu comportamento na presença de possíveis falhas (HASAN; PATEL; TAHAR, 2011). A fim de guiar o processo de *design* de projeto desses componentes, buscando obter as saídas lógicas para as quais o projeto do circuito foi idealizado, é necessário que sejam desenvolvidas ferramentas que possam avaliar, com eficiência e acurácia, a confiabilidade dos mesmos. Contudo, o processo de avaliar a confiabilidade exata de um circuito integrado, envolve ou metodologias exaustivas ou métodos com complexidade exponencial, ou seja, diretamente relacionada com o tamanho do circuito a ser analisado. Para estimar a confiabilidade de um circuito combinacional qualquer, utilizando uma metodologia exaustiva, a complexidade total estará relacionada com a Equação 1, onde  $N_g$  é o número de portas lógicas e  $N_{in}$  refere-se ao número de entradas do circuito (XIAO; CHEN, 2014). Isso quer dizer que, dependendo do tamanho do circuito a ser analisado, o poder computacional exigido pode inviabilizar o processo de análise. A seguir serão apresentados diversos conceitos e métodos de análise relacionados à confiabilidade em circuitos digitais.

$$O(N_g.2^{(N_{in}+N_g)}) \tag{1}$$

### 2.1 Definições e Métricas

Considerando todas as informações descritas até agora, é possível determinar que conhecer a confiabilidade de um circuito pode auxiliar no processo de concepção do projeto destes dispositivos. Quando se trata de confiabilidade em sistemas, no geral, são utilizados os termos R e R(t), onde a confiabilidade será a probabilidade de um sistema funcionar corretamente no intervalo [0,t], onde R(0)=1 (LALA, 2001). A métrica utilizada para a confiabilidade em sistemas eletrônicos é a taxa de falhas, a qual é representada pelo símbolos  $\lambda$  ou  $\lambda(t)$  e, nada mais é do que a frequência que o sistema falha em um determinado período de tempo (FINKELSTEIN, 2008). Contudo, dado o número de fatores

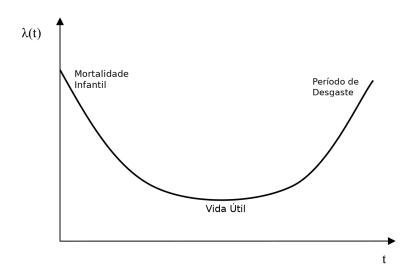

que podem influenciar a taxa de falhas de um componente eletrônico, um valor preciso é difícil de ser determinado, o que leva à aplicação de métodos probabilísticos, onde são consideradas informações de diferentes fontes, tais como simulação e testes (FRANCO, 2008). Além disso, a taxa de falhas de sistemas eletrônicos é variável, desde o período de utilização inicial até o de desgaste (*wear-out*), e este comportamento é modelado como diagrama da "curva da banheira" (*bathtube curve - BC*), a qual está representado na Fig. 3. Neste diagrama, a taxa de falhas inicial é alta devido ao grande número de componentes que estão sendo usados pela primeira vez, e o termo utilizado para definir este período é "mortalidade infantil". Em seguida existe um período com uma taxa de falhas quase constante, ao longo da "vida útil" do sistema. Por último, ocorre o período de "desgaste" do sistema, onde a taxa de erros sobe. Isso se deve aos fatores de fatiga e de degradação dos componentes do sistema (FINKELSTEIN, 2008).

Figura 3: Diagrama da Curva da Banheira, adaptado de (FINKELSTEIN, 2008)

Considerando somente o período de vida útil do sistema, a taxa de falhas será constante, ou seja,  $\lambda = \lambda(t)$ . Assim, a confiabilidade do sistema pode ser definida pela Equação 2 (FRANCO, 2008).

$$R(t) = e^{-\lambda t} \tag{2}$$

Por outro lado, uma métrica mais utilizada para fazer comparações entre confiabilidades de diferentes sistemas é o **MTBF** (*Mean-Time Between Failure* (LIENIG; BRU-EMMER, 2017), o qual tem uma relação recíproca com a taxa de falhas e é expressa em horas. Nas Equações 3 e 4, estão descritas, respectivamente, como obter o MTBF a partir da taxa de falhas e a equação de confiabilidade adaptada para o MTBF.

$$MTBF = \frac{1}{\lambda} \tag{3}$$

$$R(t) = e^{-\frac{t}{MTBF}} \tag{4}$$

Outra métrica utilizada na indústria de semicondutores é o **FIT** (*Failure in Time*), o qual significa a quantidade de falhas em 10<sup>9</sup> horas (LIENIG; BRUEMMER, 2017). O FIT pode ser obtido a partir do MTBF, conforme a Equação 5 (ICHINOMIYA et al., 2010).

$$FIT = \frac{10^9}{MTBF} \tag{5}$$

#### 2.2 Simulação e Injeção Física de Falhas

Simulação e injeção física de falhas podem ser dividas em duas técnicas baseadas na necessidade de fabricação do circuito. A Simulação de Falhas é uma técnica simples e intuitiva para se estimar a confiabilidade de um circuito. O processo consiste em selecionar um nodo, que dependendo da granularidade utilizada na análise, pode ser desde um bloco no circuito até um transistor individual (HSUEH; TSAI; IYER, 1997). Selecionado o nodo, a análise consiste na observação dos valores de saída do circuito em determinado período de tempo. Como base de comparação, geralmente se utiliza, em paralelo, uma segunda versão do circuito livre de falhas. Assim a simulação verifica quais nodos estão provocando desvios nos valores de saída. É necessário destacar que o tempo consumido em simulações de injeção de falhas é alto. Isso se deve à simulação ter de lidar com todos cenários possíveis, incluindo a combinação de falhas e todas os valores de entrada possíveis do circuito. Assim, dependendo do tamanho do circuito, esta abordagem se torna inviável.

Técnicas de injeção necessitam de uma amostra do circuito, ou seja, é necessário que o circuito seja fabricado. O procedimento de estimar a confiabilidade por meio desta técnica é expor o circuito a fatores que podem causar falhas. Como é necessário um processo de fabricação e construção de um ambiente fisicamente simulado, o custo desta técnica é elevado e não trivial. Um grande exemplo do uso deste tipo de técnica pode ser encontrado em (PARTRIDGE; HALL; HANLEY, 1965), onde é descrito como os circuitos da missão Apollo da NASA foram submetidos a testes e simulações.

#### 2.3 Simulação de Monte Carlo

A ideia de utilizar a aleatoriedade para determinar algo foi revolucionária. É possível rastrear cientistas que fizeram uso desde o século 18. Contudo, o método de Monte Carlo como é conhecido e reconhecido atualmente, foi utilizado na época da Segunda Guerra Mundial, no projeto Manhattan, por John Von Neumann e Stanislaw Ulam para o desenvolvimento de armamento nuclear (HARRISON, 2010). Desde então, a técnica é utilizada por diversos profissionais de várias áreas, como finanças, gerenciamento de

projetos, energia, indústrias, engenharia, pesquisa e desenvolvimento, seguros, petróleo e gás, transportes e meio ambiente. A simulação de Monte Carlo é uma técnica computacional que possibilita levar em conta o risco em análises quantitativas e tomadas de decisão fornecendo uma gama de resultados possíveis e as probabilidades de ocorrências desses resultados de acordo com a ação escolhida como decisão. As desvantagens que envolvem o método são o seu alto custo computacional e a inexatidão dos resultados, pois estes são baseados no modelo de entrada do método.

Com relação à estimativa de confiabilidade de circuitos lógicos, a simulação de Monte Carlo pode lidar com parâmetros randômicos, o que pode ser uma grande vantagem perante outros métodos, conforme pode ser visto em (LIU; CAI, 2017), o qual propõe um modelo para obter a confiabilidade de um circuito combinacional na presença de falhas do tipo SET. Existem diversas formas de conceber um modelo de simulação Monte Carlo, mas para fins de confiabilidade de circuitos, todas soluções irão convergir na expressão representada na Equação 6, onde  $N_o$  é o número total de amostragem e  $N_e$  é o número de resultados não esperados.

$$R_{circuit} = 1 - \frac{N_e}{N_o} \tag{6}$$

## 2.4 Abordagens Analíticas

Existem diversos métodos que estimam a confiabilidade de um circuito por meio de abordagens analíticas. A maioria deles leva em conta dados probabilísticos (FRANCO, 2008). A probabilidade é uma forma de se lidar e modelar grande parte das falhas em circuitos lógicos. Assim sendo, o método "Modelo de Portas Probabilísticas - PGM" é baseado análise de confiabilidade por meio do tratamento probabilístico de sinais (HAN et al., 2014). A probabilidade de um sinal de entrada ou saída, geralmente, é definida pela probabilidade de o sinal ser um "1" lógico. Levando em conta tais premissas, o método PGM foi proposto por (HAN et al., 2011) onde é utilizada a Lógica Probabilística para modelar e estimar a confiabilidade do circuito lógico.

O método PTM (Matrizes de Transferência Probabilística) visa estimar a confiabilidade de um circuito de forma precisa, tendo sido proposto por (PATEL; HAYES; MARKOV, 2003). É um método que tem um problema de escalabilidade, sendo assim, é um bom modelo para analisar circuitos pequenos, mas se torna computacionalmente inviável quando se quer trabalhar com circuitos com mais de 2 dezenas de portas lógicas. Mesmo assim, este método foi o escolhido para ser analisado e implementado neste trabalho, pois quando se trabalha com escalas nanométricas, a precisão pode ser um grande diferencial.

Outro método que pode ser utilizado para estimar a confiabilidade de um circuito é o método "*Probabilistic Model Checking* - PMC", o qual é um procedimento de verificação se uma certa probabilidade satisfaz uma probabilidade especificada. O PMC foi utilizado

para a análise de confiabilidade em (BHADURI et al., 2007). Neste método os circuitos são descritos em cadeias de Markov em tempo discreto ou DTMC, o que segundo (SI-EWIOREK; SWARZ, 2017) é a estrutura mais apropriada para modelar sistemas digitais. A confiabilidade de um circuito é obtida calculando a probabilidade de atingir estados de DTMC específicos, onde tais estados representam os valores booleanos corretos nas saídas do circuito para uma certa distribuição de probabilidade nas entradas. Em 1999 um grupo de pesquisas da Universidade de Birmingham criou o PRISM, acrônimo para *Probabilistic Symbolic Model Checker*. O *software* utiliza o método PMC para dar suporte à análise de três tipos de modelos probabilísticos (KWIATKOWSKA; NORMAN; PARKER, 2004): DTMC, CTMC(continuous-time Markov chains) e MDP(Markov decision processes).

Por fim, o método "Signal Probability Reliability - SPR" é um modelo baseado na probabilidade de um sinal assumir valores corretos e incorretos. A representação dos sinais se dá por quatro estados: 0 correto e incorreto e 1 correto e incorreto. Os quatro estados são representados por uma matriz de ordem 2 x 2. O método não trata as correlações de sinais, ou seja, na presença de caminhos reconvergentes (fanouts), sinais iguais são tratados de formas diferente ao mesmo tempo, invalidando o resultado final de confiabilidade (FRANCO et al., 2008).

A PTM foi um dos métodos escolhidos para este trabalho. Por ser um método exato de estimativa de confiabilidade, pode ser usado para avaliar outros métodos. Assim, outro método escolhido foi o SPR que além de ter sido desenvolvido baseado nas características da PTM, é um método com complexidade linear. Esta característica do SPR pode tornar possível a sua utilização para estimar a confiabilidade e lidar com problemas de escalabilidade em circuitos grandes.

## 3 OS MÉTODOS PTM E SPR

Neste capítulo serão descritos, com maior aprofundamento teórico, métodos que estimam a confiabilidade de circuitos digitais por abordagem analítica. Além disso, esses métodos foram utilizados para atingir os objetivos deste trabalho.

A análise de confiabilidade em componentes eletrônicos pode ser divida em dois aspectos: predição e avaliação (PAGLIARINI, 2013). Os dois aspectos são igualmente importantes no processo de design de circuitos, pois a avaliação da confiabilidade permite a validação e refinamentos dos modelos de confiabilidade preditivos. O contexto deste trabalho será o estudo de confiabilidade pelo aspecto da predição.

#### 3.1 Matriz de Transferência Probabilística

A abordagem do método Matriz de Transferência Probabilística (*Probabilistic Transfer Matrix* - PTM) é de estimar a confiabilidade de um circuito de forma exata, pois representa, por meio de matrizes, todas as possibilidades de entrada, saída e operação de um circuito. O método foi proposto por Patel et al (PATEL; HAYES; MARKOV, 2003), o qual foi amplamente explorado por Krishnaswamy et al (KRISHNASWAMY et al., 2005). A ideia central da PTM, é correlacionar as entradas e saídas de um circuito, considerando sua topologia e confiabilidade individual de cada porta (FRANCO, 2008).

Em uma matriz PTM, a relação entre linhas e colunas corresponde à probabilidade de uma combinação de entrada (linha) gerar uma combinação de saída (coluna). Nesse sentido, é possível inferir que ao somar todos os elementos de uma linha, o resultado deverá ser 1. Tendo em vista que a matriz é formada por todas as combinações de entrada e de saída de uma porta ou de todo um circuito, a ordem da matriz resultante é dada pela fórmula  $2^x \times 2^y$ , onde x é o número de entradas e y é o número de saídas.

A matriz PTM individual de cada porta está diretamente relacionada com a respectiva tabela verdade. Enquanto na tabela verdade são demonstrados os valores gerados pela função lógica da porta, na PTM são demonstradas as probabilidades da porta gerar os valores 0 e 1 na sua saída, considerando possíveis falhas de operação da porta. No método a matriz PTM de uma porta lógica possui duas variáveis: "q" que representa a

confiabilidade da porta, e "1-q" que, como pode ser observado, é o complemento da confiabilidade, ou seja, a probabilidade da porta gerar um valor errado. Outro ponto importante do método é a existência de Matriz de Transferência Ideal (*Ideal Transfer Matrix* - ITM), a qual representa o comportamento ideal da porta lógica ou do circuito, ou seja, sem a presença de falhas. Na Figura 4 estão representadas uma tabela verdade, uma matriz ITM e uma matriz PTM de uma porta lógica *AND* de duas entradas, as quais demonstram a forma como são obtidos os elementos para os futuros cálculos.

| Input | Input | Output |  |

|-------|-------|--------|--|

| Α     | В     | Υ      |  |

| 0     | 0     | 0      |  |

| 0     | 1     | 0      |  |

| 1     | 0     | 0      |  |

| 1     | 1     | 1      |  |

| (a)   |       |        |  |

|                      | 0 | 1           |  |  |

|----------------------|---|-------------|--|--|

| 00                   | 1 | 0           |  |  |

| 00<br>01<br>10<br>11 | 1 | 0<br>0<br>0 |  |  |

| <b>10</b>            | 1 | 0           |  |  |

| 11                   | 0 | 1           |  |  |

|                      | • | •           |  |  |

| (b)                  |   |             |  |  |

$$\begin{array}{c|cc}

\mathbf{0} & \mathbf{1} \\

\mathbf{00} & q & 1-q \\

\mathbf{01} & q & 1-q \\

\mathbf{10} & q & 1-q \\

\mathbf{11} & 1-q & q

\end{array}$$

(c)

Figura 4: Relação entre Tabela Verdade e Matriz PTM: (a)Tabela Verdade e Matrizes (b)ITM e (c)PTM de uma Porta *AND*

Outro elemento básico a ser levado em consideração pelo método são os fios condutores entre as portas lógicas. Esses elementos também são representados na forma de matrizes. Contudo, o método considera que a probabilidade de falha entre interconexões é nula, ou seja, é considerada apenas a propriedade de condução dos valores lógicos. A construção da matriz segue as mesmas características da matriz ITM anteriormente introduzida. Alguns arranjos de interconexões e suas respectivas matrizes estão representados na Fig. 5.

Figura 5: Exemplos de arranjos de fios condutores e suas respectivas matrizes (FRANCO, 2008)

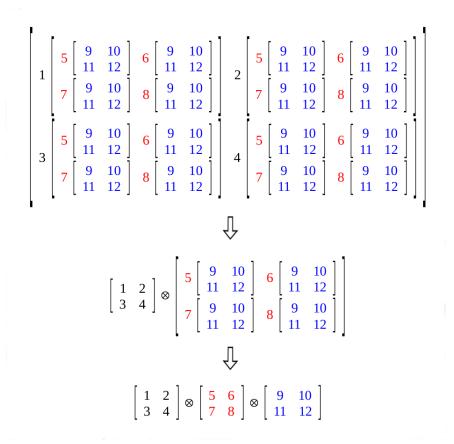

No método PTM, as principais operações entre as matrizes são o tensor de Kronecker e a multiplicação de matrizes, onde a aplicação de uma ou de outra dependerá da disposição entre as portas do circuito. Em termos gerais, quando se tem uma disposição em paralelo é utilizado o tensor de Kronecker, pois este expande as combinações entre as matrizes. No caso de disposições em série, é utilizada a multiplicação de matrizes.

É importante destacar a necessidade da caracterização topológica do circuito, visto que a abordagem PTM considera a divisão do circuito em dois tipos de níveis: o de portas

e o de interconexões (fios condutores). No nível de portas, como o próprio nome já sugere, são consideradas as portas que possuem possuem a mesma profundidade lógica. Já o nível de interconexões está relacionado com a topologia dos fios condutores entre a entrada e o primeiro nível de portas e entre os demais níveis de portas subsequentes.

Quando se trata de nível de portas, vale destacar que, uma interconexão poderá ser considerada uma porta. Isto ocorre, por exemplo, quando duas portas estão separadas por um ou mais níveis de profundidade. Em um nível de porta, todas as portas estão em uma disposição paralela. Sendo assim, a matriz PTM dos níveis de portas é obtida por meio da aplicação do tensor de Kronecker entre todas as portas do respectivo nível, respeitando a ordem vertical das portas.

Todos os níveis de portas são interligados por níveis de interconexão. Porém, nem todos os níveis de interconexão são levados em consideração nos cálculos. Como exemplo, pode ser citado um arranjo de quatro condutores de entrada abcd, onde cada letra é um rótulo de um respectivo fio, formando um nível de interconexão. Se for considerado que na entrada e na saída deste nível a topologia permanece a mesma, ou seja, o nível possui a entrada abcd e saída abcd (uma disposição paralela), este nível de interconexão não causará efeito nos cálculos de confiabilidade. Contudo, se existe um nível de interconexão com a entrada abcd e saída abbcd, isso significa que ocorreu uma mudança topológica do condutor **b**, o qual se dividiu em um fanout, e neste caso em específico, a matriz gerada por este nível de interconexão deve ser considerada para se obter a confiabilidade exata de todo o circuito. A matriz gerada no nível também terá uma ordem dada pela fórmula  $2^x \times 2^y$ , onde x é o número de entradas, que neste caso são quatro, e y é o número de saídas, ou seja, cinco (abbcd) no exemplo citado. Os elementos desta matriz serão os valores "0" ou "1", os quais estarão relacionados com as combinações de entrada e saída corretos. Nesse sentido, a primeira linha desta matriz, a qual tem o endereço "0000" (a = 0, b = 0, c = 0, d = 0), a única coluna correta será a "00000" (a = 0, b = 0, b = 0, c = 0, d = 0). Portanto o elemento  $0 \times 0$  desta matriz de interconexão terá o valor "1" e todos os outros elementos desta linha serão "0".

Já foi visto que quando há uma disposição paralela de elementos no circuito, aplica-se o tensor de Kronecker. Quando os elementos estão em série, a multiplicação de matrizes é aplicada. Sendo assim, para gerar a matriz PTM de todo o circuito, é necessário multiplicar as matriz tanto de portas quanto de interconexões entre si.

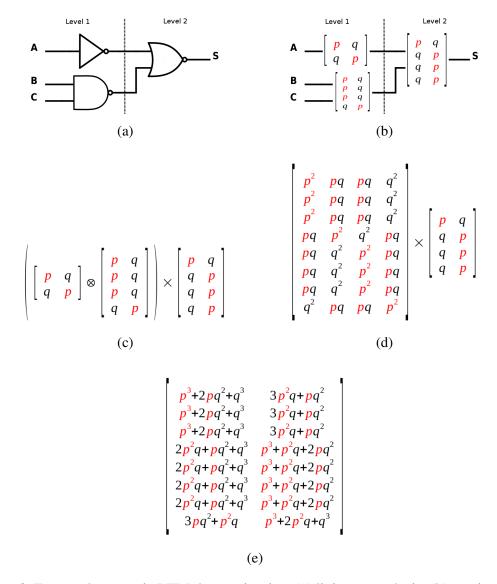

Apresentados os componentes básicos do método, é possível seguir com a forma de determinar a confiabilidade de um circuito. Para tanto, o primeiro passo é determinar quais são os níveis do circuito a ser analisado. A Figura 6 demonstra todos os passos para se obter a matriz PTM de um circuito. Após a divisão do circuito em níveis (6a), as portas são vinculadas às suas respectivas matrizes PTM (6b). Pode ser visto que, dada a topologia do circuito, as duas matrizes de interconexão (1 - entrada do circuito; 2 - entre os dois níveis de porta) serão desconsideradas nos cálculos, visto que não apresentam

alteração das disposições dos fios condutores. Identificados os dois níveis de porta, é possível descrever a equação que formará a matriz PTM de todo o circuito (6c). A equação deve respeitar a ordem dos sinais no circuito. Assim, primeiro se obtém a matriz do primeiro nível, aplicando o tensor de Kronecker (6d), em seguida se identifica o próximo nível, o qual nesse exemplo é composto por apenas uma porta lógica e, por fim, multiplicase as matrizes dos dois níveis, obtendo, neste caso, a matriz de todo o circuito (6e).

Figura 6: Formando a matriz PTM de um circuito: (a)divisão em níveis, (b)matrizes PTM das portas, (c)operações do método, (d)resolução do tensor de Kronecker e (e)matriz PTM do circuito gerada pela multiplicação de todas as matrizes dos níveis

Tendo a matriz PTM de todo o circuito, o próximo passo é a forma de se obter o valor de confiabilidade. Para tanto, é necessário obter os valores da matriz ITM, a qual terá as mesmas dimensões da matriz PTM de todo o circuito. Por outro lado, a ITM refletirá o comportamento do circuito livre de qualquer falha. Assim, são definidos duas equações que podem ser utilizadas para determinar a confiabilidade do circuito. Caso as probabilidades dos sinais sejam distintas entre si, a Expressão (7) deve ser utilizada.

Geralmente, as entradas de um circuito possuem as mesmas probabilidades. Além disso, também são consideradas livres de falhas. Assim, se este for o caso, é possível utilizar a Expressão (8) para obter a confiabilidade do circuito.

$$R_{PTM} = \sum_{ITM_c(i,j)=1} p(j|i)p(i)$$

(7)

$$R_{PTM} = \frac{1}{2^n} \sum_{ITM_c(i,j)=1} p(j|i)$$

(8)

O acumulador presente em ambas expressões refere-se aos elementos da matriz PTM que tem uma relação com os elementos iguais a **1** na matriz ITM. Esta relação pode ser vista na Fig. 7, a qual é a representação da matriz PTM e ITM do circuito presente na Fig. 6. O método PTM é um modo exato de estimar a confiabilidade de um circuito, mas sua complexidade é exponencial ao número de portas em um mesmo nível, o que o torna impraticável de ser utilizado em sua forma original.

$$ITM_c = egin{bmatrix} 1 & 0 \ 1 & 0 \ 1 & 0 \ 1 & 0 \ 1 & 0 \ 1 & 0 \ 1 & 0 \ 1 & 0 \ 1 & 0 \ 1 & 0 \ 1 & 0 \ 1 & 0 \ 1 & 0 \ 1 & 0 \ 1 & 0 \ 1 & 0 \ 1 & 0 \ 1 & 0 \ 0 & 1 \ \end{bmatrix} \hspace{1.5cm} PTM_c = egin{bmatrix} p^3 + 2pq^2 + q^3 & 3p^2 + pq^2 \ p^3 + 2pq^2 + q^3 & 3p^2 + pq^2 \ p^3 + 2pq^2 + q^3 & p^3 + p^2q + 2pq^2 \ 2p^2q + pq^2 + q^3 & p^3 + p^2q + 2pq^2 \ 2p^2q + pq^2 + q^3 & p^3 + p^2q + 2pq^2 \ 2p^2q + pq^2 + q^3 & p^3 + p^2q + 2pq^2 \ 2p^2q + pq^2 + q^3 & p^3 + p^2q + 2pq^2 \ 3pq^2 + p^2q & p^3 + 2p^2q + q^3 \ \end{bmatrix}$$

Figura 7: Relação PTM e ITM

#### 3.2 Confiabilidade pela Probabilidade de Sinais

O método SPR e todas as suas variantes se baseiam nas matrizes do tipo PTM. Por outro lado, o SPR visa reduzir o problema com o tamanho das matrizes. Isso o torna escalável, ou seja, pode ser aplicado mesmo em circuitos grandes, diferente do método PTM. A premissa do SPR é de que é possível estimar a confiabilidade de um circuito por meio da propagação das probabilidades dos sinais da entrada até a saída. A metodologia considera que a ocorrência de uma saída correta pode ser determinada pela computação cumulativa dos efeitos de múltiplas falhas nos sinais do circuito. Levando em consideração todas as possíveis interações dos sinais e portas propensos a falhas, o método de probabilidade de sinais os modela obtendo as probabilidades dos sinais subsequentes e, por fim, a confiabilidade de todo o circuito.

Assim como na PTM, operações com matrizes são utilizadas para representar as probabilidades dos sinais. Cada matriz de sinal possui quatro estados: 0-correto, 0-incorreto,

1-correto e 1-incorreto (FRANCO et al., 2008). Uma representação da matriz e as respectivas posições de cada estado, podem ser observadas na Fig. 8.

$$SPR signal = egin{bmatrix} P("0"correto) & P("1"incorreto) \ P("0"incorreto) & P("1"correto) \end{bmatrix}$$

Figura 8: Matriz de probabilidade de sinal

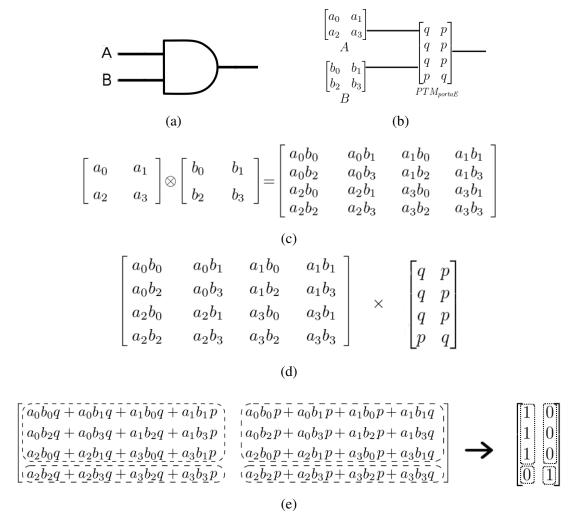

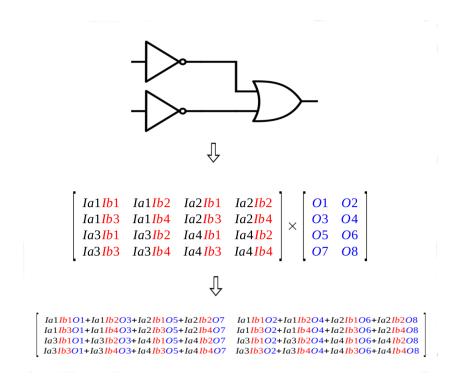

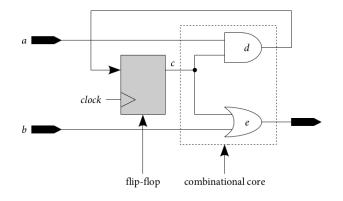

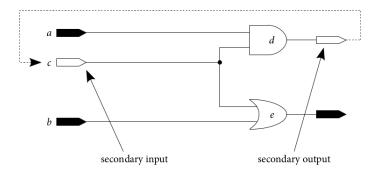

O processo de estimativa de confiabilidade pelo método SPR, diferente do método PTM, se dá de forma sequencial, ou seja, propagando e calculando as probabilidades dos sinais desde as entradas até as saídas do circuito. Assim, é importante demonstrar como os sinais se propagam por uma porta lógica. Como exemplo, o procedimento é ilustrado na Fig. 9, onde são consideradas duas entradas primárias em uma porta do tipo *AND* lógica.

A Fig. 9b demonstra como é o processo inicial para se obter a confiabilidade do sinal de saída de uma porta AND lógica, a qual é representada na Fig. 9a. Analisando as duas imagens em conjunto, fica claro qual é a relação entre a topologia da porta com as matrizes do método. Assim, o primeiro cálculo a ser feito é obter uma matriz de probabilidade entre os dois sinais de entrada. Como na PTM, tendo em vista que os dois sinais, obviamente, estão em paralelo, o tensor de Kronecker deve ser aplicado, e esse passo pode ser observado na Fig. 9c. A matriz PTM da porta é utilizada para modelar como as probabilidades irão se propagar pela mesma. Mais uma vez, fazendo alusão à PTM, já que os sinais estão em série com a porta, a operação de matriz a ser utilizada é a multiplicação, e a representação se encontra na Fig. 9d. A matriz resultante será uma matriz  $2^x \times 2^y$ , onde X e Y são respectivamente o número de entradas e saídas da porta. Contudo, a ordem de uma matriz de probabilidade de sinal, no método SPR, sempre será  $2 \times 2$ . Portanto, a consolidação da matriz do sinal de saída é feita utilizando a matriz ITM da porta lógica. Esta relação está demonstrada na Fig. 9e. Por meio da ITM, é possível agrupar quais combinações de entrada resultarão em cada um dos quatro estados do sinal. Após agrupar, os elementos são somados e posicionados conforme a defição de matriz de probabilidade de sinal do método.

No exemplo utilizado, após obter a matriz do sinal de saída da porta, a confiabilidade do sinal será a soma das probabilidades dos estados corretos, ou seja, a soma entre os elementos das posições  $1 \times 1$  e  $2 \times 2$ . Para se estimar a confiabilidade de todo o circuito, além de fazer a sequência de passos descritos para cada uma das portas, é necessário fazer uma junção entre as confiabilidades dos sinais de saída do circuito, conforme é expressado na Equação 9, onde  $R_j$  está relacionado à  $j^{th}$  saída do circuito a ser estimado.

$$R_{SPR} = \prod_{j=0}^{m-1} R_j \tag{9}$$

Figura 9: Passos para estimar a confiabilidade do sinal de saída de uma porta *AND* com o método SPR: (a) porta E com duas entradas primárias, (b) matrizes das entradas e matriz PTM da porta, (c)aplicação do tensor de Kronecker nas entradas da porta, (d)multiplicação da matriz referente às entradas com a matriz PTM da porta e (e) matriz resultante da multiplicação com os valores que irão compor a matriz do sinal de saída

O modelo SPR é um método rápido para estimar a confiabilidade de um circuito, pois sua complexidade é linear ao número total de portas lógicas do circuito, ou seja, O(G). Os valores gerados pela abordagem são exatos desde que o circuito não possua *fanouts* reconvergentes. Essa característica é a que inviabiliza o método, pois as derivações em fios condutores é comum em circuitos digitais.

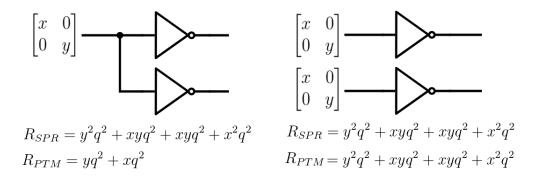

A fim de demonstrar como o SPR se comporta na presença de *fanouts* reconvergentes, foi elaborada a Fig. 10. Nesta imagem estão presentes duas formas distintas de duas portas lógicas do tipo inversor, onde à esquerda as entradas das portas compartilham o mesmo sinal de entrada, ou seja, existe um *fanout*. Na Figura à direita, as portas recebem entradas independentes. No intuito de explicitar o problema do SPR, foi utilizada a PTM como base exata de comparação. Analisando a imagem, é possível inferir que o método SPR processa o sinal de *fanout* como se o mesmo representasse dois sinais distintos.

Contudo, isso faz com que sejam considerados valores redundantes de probabilidade, o que ao final irá gerar valores de confiabilidade nulos.

Figura 10: O problema do SPR

#### 3.2.1 SPR Multi-Pass

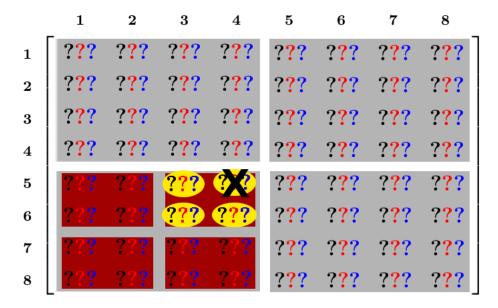

Tendo em vista a forma como o método SPR lida com *fanouts* reconvergentes, uma nova abordagem foi proposta por (FRANCO et al., 2008). Essa abordagem foi denominada SPR *Multi-pass* ou simplesmente "SPR-MP". Esta variação do SPR foi baseada no fato de que cada *fanout* contribuí de forma diferente nas probabilidades dos sinais e na confiabilidade final do circuito. Assim, o algoritmo do SPR-MP corrige as probabilidades nos sinais, propagando probabilidades distintas em múltiplas iterações. Contudo, um resultado exato somente é obtido, se todos os estados de todos os *fanouts* forem considerados.

$$R_c = \sum_{f=1}^{4^F} R_{c(f)} \tag{10}$$

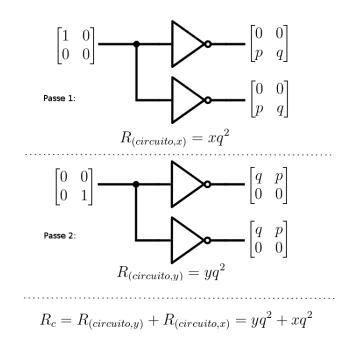

A forma de cálculo da confiabilidade do circuito de acordo com o SPR-MP pode ser observada na Expressão 10, onde  $4^F$  está relacionado aos quatro estados de uma matriz de sinais sobre o número de *fanouts*; f está relacionado ao estado de *fanout* corrente. Na Fig. 11 está representado o comportamento do algoritmo do SPR-MP. É possível observar que cada estado do *fanout* representa um ciclo em todo o circuito. No final, a confiabilidade de cada ciclo é somada. Vale ressaltar que o expressão encontrada é a mesma da PTM na Fig. 10.

A complexidade do método SPR-MP é exponencial em relação ao número total de *fanouts*. Isso pode tornar o método inviável em circuitos reais. Assim, outra forma de racionalizar a quantidade de ciclos do algoritmo, pode ser utilizar um limite de valores de probabilidade próximas a 0. Isso significa que passadas com probabilidades de estados de *fanouts* que sejam iguais ou menores ao limite definido, não serão executadas pelo algoritmo.

Figura 11: Exemplo de aplicação do algoritmo SPR-MP

#### 4 FERRAMENTA DESENVOLVIDA

#### 4.1 Descrição da Ferramenta

A fim de atingir os objetos propostos neste trabalho, foi desenvolvida uma ferramenta que implementa os métodos PTM, SPR e SPR-MP. A linguagem de programação escolhida no desenvolvimento foi JAVA, devido a familiaridade do autor com a linguagem e a utilização desta linguagem em outros projetos no grupo de pesquisas. O circuito é caracterizado na ferramenta através de uma descrição no padrão HDL (*Hardware Description Language*) - Verilog. A partir da descrição HDL do circuito, uma estrutura de dados é criada, modelando características básicas do circuito, tais como: quantidade total de portas e sinais, tipos de portas utilizadas no circuito, níveis lógicos, dentre outros.

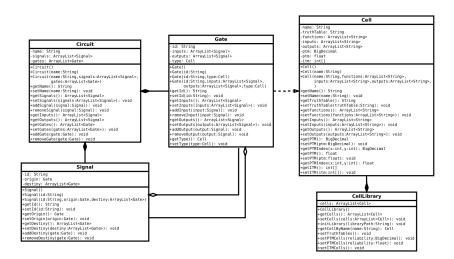

Um dos principais princípios do paradigma da programação orientada a objetos é o foco no reuso dos códigos gerados (BRUEGGE; DUTOIT, 2004). Com isso em mente, a estrutura de dados que representa o circuito foi desenvolvida para ser a mais genérica possível, ou seja, que se adaptasse a outras demandas que envolvam circuitos lógicos. Nesse sentido, na Fig. 12 está ilustrado o diagrama de classes desta estrutura básica.

Conforme o diagrama, um objeto "Circuito" (Circuit) é composto por objetos "Porta" (Gate) e "Sinal" (Signal). A relação entre sinais e portas lógicas se deu aplicando o

Figura 12: Diagrama de classes da estrutura básica que representa um circuito lógico

Figura 13: Diagrama de classes da estrutura especializada para os métodos PTM e SPR

conceito de "composição" entre as classes "Porta" e "Sinal", e assim foi possível modelar as entradas e saídas de uma porta lógica e, por sua vez, a origem e destino de um sinal lógico. Ainda sobre a classe "Porta" foi modelada uma relação de dependência com a classe "Célula" (Cell), a qual contém os atributos do tipo da porta lógica. Por fim, a classe "Biblioteca de Células" (CellLibrary) é utilizada para lidar com as células criadas a partir do arquivo externo que conterá todos os tipos de células.

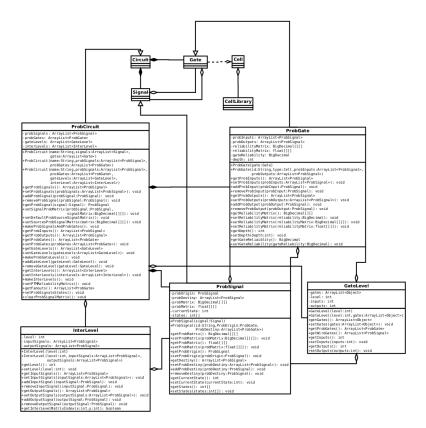

Contudo, para o cálculo da confiabilidade, utilizando os métodos propostos, foi necessário especializar e criar classes que modelassem as peculiariedades de cada um. Assim, chegou-se ao diagrama de classes representado na Fig. 13. O conceito de herança foi aplicado às três classes básicas: "Circuito", "Porta" e "Sinal". Foram introduzidos atributos que pudessem lidar com as probabilidades individuais de portas e sinais. No tocante à nova classe que representa uma porta lógica, pode parecer que há redundância das probabilidades com a classe "Célula".

Com a possibilidade de cada porta poder possuir uma probabilidade individual, experimentos que envolvam a análise individual de cada porta são possíveis. A justificativa pode ser a mesma com relação à nova classe que representam os sinais do circuito. As classes "Nível de Gate" (GateLevel) e "Nivel de Interconexão" (InterLevel) representam a topologia do circuito, a qual é uma característica importante, principalmente para o método PTM. Em um objeto "Nível de Porta" estão contidos as portas e sinais relacionais a um determinado nível lógico do circuito. Já um objeto "Nível de Interconexão"

modela os sinais que estão entre os níveis de portas de um circuito. Este objeto facilita a verificação do comportamento do sinais, principalmente com relação às derivações e cruzamentos entre os mesmos.

Uma característica que é possível destacar sobre a ferramenta é a não necessidade de *softwares* externos para os cálculos dos métodos. Isto geraria uma dificuldade maior para o desenvolvimento, pois existem *softwares* consolidados para fazer cálculos, tais como *Matlab* e *Scilab*. Todavia, a flexibilidade em customizar as funcionalidades se torna um diferencial nos estudos.

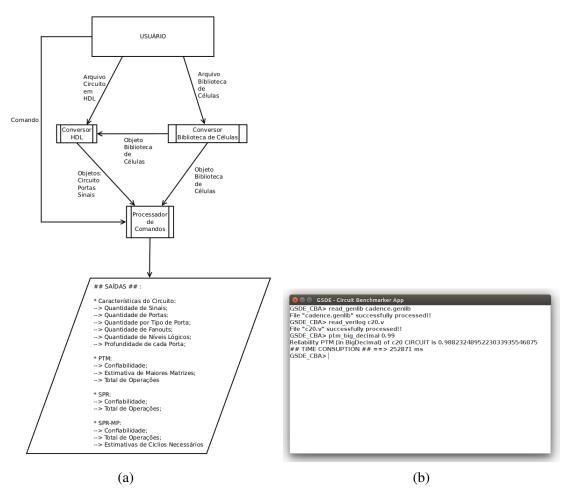

Um diagrama de funcionamento da ferramenta é demonstrado na Figura 14a. Como é possível visualizar, houve uma preocupação em utilizar diferentes tipos de dados a fim de verificar a influência de cada um no desempenho final dos métodos principais. Os parâmetros básicos necessários para se estimar a confiabilidade de um circuito, pela ferramenta são: (1) descrição do circuito em Verilog, contendo entradas, saídas e ligações entre as portas; (2) biblioteca de células na qual o circuito foi sintetizado; (3) a confiabilidade da tecnologia, ou seja, o valor de confiabilidade que será considerado em todas as portas lógicas do circuito. A Fig. 14b mostra o terminal da ferramenta sendo utilizado.

Figura 14: Ferramenta desenvolvida: (a)Funcionamento básico da ferramenta desenvolvida e (b)*Print screen* do terminal gerado pela ferramenta

Segundo (KRISHNASWAMY et al., 2005), o método PTM extrai a confiabilidade exata de um circuito. Por isso, a PTM será utilizada como base nas comparações. Na primeira implementação do método foi utilizada a biblioteca EJML, a qual utiliza em sua estrutura de dados valores do tipo "double" em JAVA. Contudo, para utilização da ferramenta em um trabalho correlato (SCHVITTZ et al., 2018), foi necessário implementar a PTM utilizando métodos que lidassem com o tipo de dado "BigDecimal". Este tipo de dado nativo da linguagem JAVA visa a precisão. Então, ao incluir funcionalidades que pudessem lidar com BigDecimal, foi possível notar que os valores de confiabilidade gerados para os circuitos não eram iguais, em termos de precisão. Assim, o próximo passo foi desenvolver funcionalidades que lidassem com diferente tipos de dados, neste caso o BigDecimal e o float. Não foram desenvolvidas apenas funcionalidades que estimam a confiabilidade de circuitos. Visto que, conforme a bibliografia correlata, o grande problema de estimar a confiabilidade são os problemas de escalabilidade. Assim, foram desenvolvidas aplicações que estimam o número de operações necessárias para o cálculo de confiabilidade, ou até mesmo, no caso da PTM, que estimam o tamanho das maiores matrizes a serem criadas. Na sequência serão relatados, de forma individual, como foram implementados os métodos PTM, SPR e SPR-MP.

#### 4.1.1 PTM

O método PTM foi o primeiro a ser desenvolvido e inserido na ferramenta. Como descrito nas seções anteriores, a PTM é baseada em operações com matrizes. Assim, nesta etapa inicial, optou-se por buscar uma biblioteca para apoiar nas representações e cálculos destas matrizes. Dentre todas as bibliotecas encontradas, a biblioteca EJML (EJML, 2017) mostrou-se mais apta a ser aplicada no escopo do trabalho, pois era do tipo *open source*, tinha ampla documentação e seu código era de simples compreensão e aplicabilidade.

Os primeiros valores de confiabilidade foram gerados com o método, a partir de circuitos equivalentes, em termos de tamanho, ao C17 do ISCAS85 *Benchmark* (BRGLEZ; FUJIWARA, 1985). O grande problema da PTM pôde ser confirmado, comprovando as limitações descritas na literatura sobre o método. Assim, foram seguidas duas linhas de implementação, uma denominada "tradicional" e outra "serializada", as quais são descritas a seguir.

#### 4.1.1.1 Implementação Tradicional

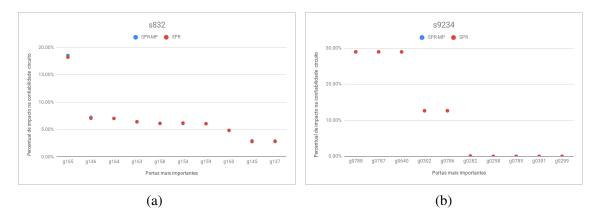

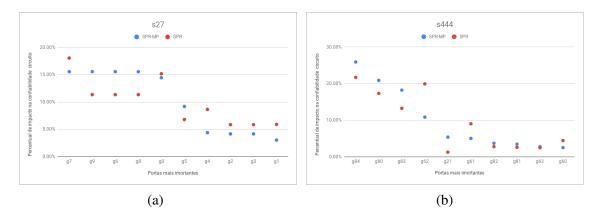

A implementação tradicional segue os mesmos procedimentos mostrados na teoria da PTM (Seção 3.1). A estrutura central nesta primeira etapa do desenvolvimento foi a representação das matrizes em sua totalidade, ou seja, as matrizes e todos os seus respectivos elementos eram criados e alocados em memória, sem qualquer tipo de compactação. Com relação às operações de multiplicação e de tensor de Kronecker, no mínimo três ma-