# UNIVERSIDADE FEDERAL DO RIO GRANDE - FURG INSTITUTO DE CIÊNCIAS COMPUTACIONAIS PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA DE COMPUTAÇÃO

Roberto Borba de Almeida

# AVALIAÇÃO DO IMPACTO DA VARIABILIDADE PVT E ENVELHECIMENTO EM CÉLULAS DE MEMÓRIA SRAM

Rio Grande 2018

### Roberto Borba de Almeida

# AVALIAÇÃO DO IMPACTO DA VARIABILIDADE PVT E ENVELHECIMENTO EM CÉLULAS DE MEMÓRIA SRAM

Defesa de dissertação do curso de pós-graduação em Engenharia de Computação apresentado ao Centro de Ciências Computacionais da Universidade Federal do Rio Grande - FURG.

Orientador: Profa. Dra. Cristina Meinhardt

Coorientador: Prof. Dr. Paulo Butzen

Rio Grande 2018

# Ficha catalográfica

A447a Almeida, Roberto Borba de.

Avaliação do impacto da variabilidade PVT e envelhecimento em células de memória SRAM / Roberto Borba de Almeida. – 2018. 85f.

Dissertação (mestrado) – Universidade Federal do Rio Grande – FURG, Programa de Pós-Graduação em Engenharia de Computação, Rio Grande/RS, 2018.

Orientadora: Dra. Cristina Meinhardt. Coorientador: Dr. Paulo Butzen.

Células de Memória 2. Nanotecnologia 3. SRAM I. Meinhardt, Cristina II. Butzen, Paulo III. Título.

CDU 004.07

Catalogação na Fonte: Bibliotecário José Paulo dos Santos CRB 10/2344

FURG MINISTÉRIO DA EDUCAÇÃO UNIVERSIDADE FEDERAL DO RIO GRANDE CENTRO DE CIÊNCIAS COMPUTACIONAIS PROGRAMA DE PÓS-GRADUAÇÃO EM COMPUTAÇÃO CURSO DE MESTRADO EM ENGENHARIA DE COMPUTAÇÃO

## DISSERTAÇÃO DE MESTRADO

### Avaliação do impacto da variabilidade PVT e envelhecimento em células de memória SRAM

Roberto Borba de Almeida

Banca examinadora:

Prof. Dr. Carlos Roberto Moratelli

Prof. Dr. Eduardo Wenzel Brião

Prof. Dr. Vagner Santos da Rosa

Profa Dra. Cristina Meinhardt

Orientadora

Pkof. Dr. Paulo Francisco Butzen

Coorientador

# LISTA DE FIGURAS

| Figura 2.1 Lei de Moore                                                                               | _ 14 |

|-------------------------------------------------------------------------------------------------------|------|

| Figura 2.2 Dispersão dos tempos de escrita (pontos amarelos) e leitura (pontos azuis) diant           | :e   |

| dos efeitos da variabilidade                                                                          | _ 16 |

| Figura 2.3 Efeitos que influenciam nas características elétricas dos dispositivos                     | _ 16 |

| Figura 2.4 Variações de temperatura em um circuito integrado                                          | _ 17 |

| Figura 2.5 Efeitos de BTI na tensão de limiar do transistor                                           | _ 18 |

| Figura 3.1 Bloco de células SRAM                                                                      | _ 20 |

| Figura 3.2 Estrutura básica de uma coluna de células                                                  | _ 21 |

| Figura 3.3 Diagrama elétrico da célula 6T                                                             | _ 22 |

| Figura 3.4 Escrita do valor '1' na célula 6T                                                          | _ 22 |

| Figura 3.5 Leitura do valor '1' na célula 6T                                                          | _ 23 |

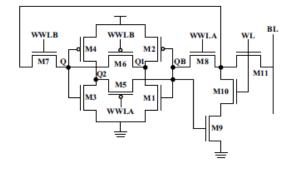

| Figura 3.6 – Células de memória (a) 5T Portless, (b) 7T, (c) ST11T, (d) 8T e (e) 8T_v2                | _ 24 |

| Figura 3.7 – Células SRAM (a) 9T_v1, (b) PG9T e (c) 9T_v2                                             | _ 25 |

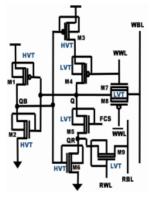

| Figura 3.8 Células SRAM (a) 11T_v1 e (b) 11T_v2                                                       | _ 26 |

| Figura 3.9 Células SRAM (a) PFC 10T, (b) 9T_v3, (c) 9T_v4 e (d) 10T.                                  | _ 27 |

| Figura 4.1 Fluxograma da metodologia de análise das células 6T e 8T                                   | _ 32 |

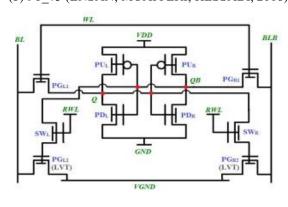

| Figura 4.2 Células 6T, 8T e 9T                                                                        | _ 33 |

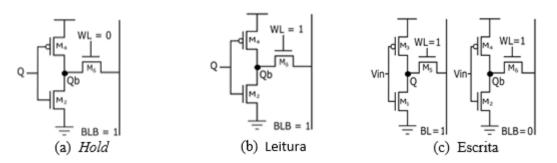

| Figura 4.3 Circuitos para a obtenção das margens HSNM (a), RSNM (b) e WSNM (c)                        | _ 35 |

| Figura 4.4 Curvas de transferência de tensão no estado de <i>hold</i> (a), leitura (b) e escrita (c)_ | _ 35 |

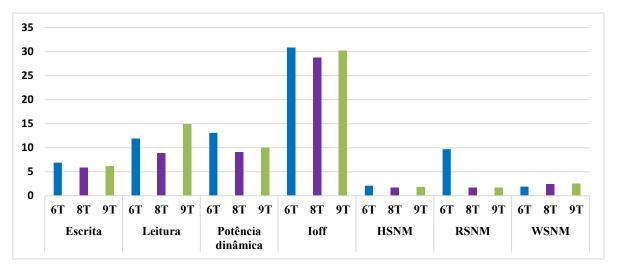

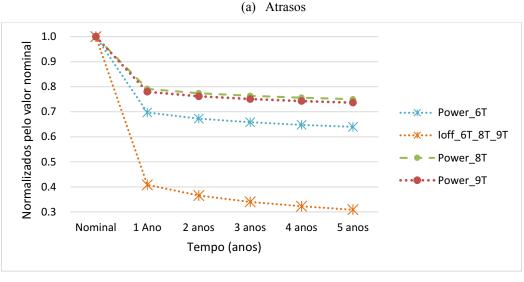

| Figura 5.1 Evolução do impacto nas tecnologias                                                        | _ 40 |

| Figura 5.2 Impacto da variabilidade de processo na tecnologia HP                                      | _ 44 |

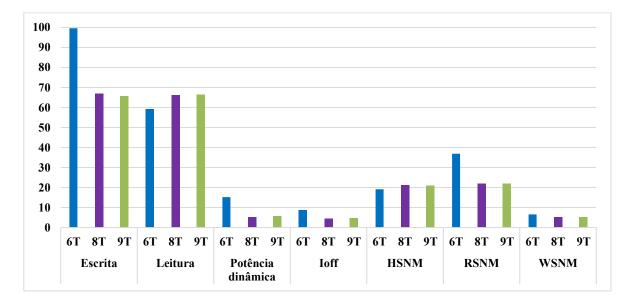

| Figura 5.3 Impacto da variabilidade de processo na tecnologia LP                                      | _ 46 |

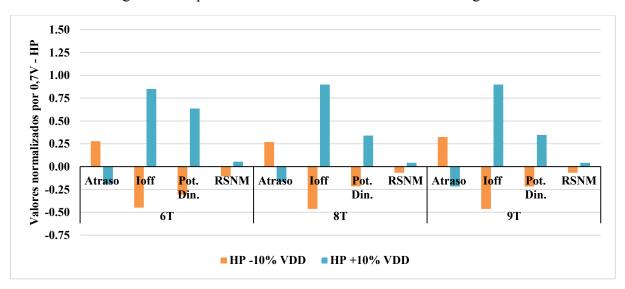

| Figura 5.4 Impacto da variabilidade de tensão na tecnologia HP                                        | _ 47 |

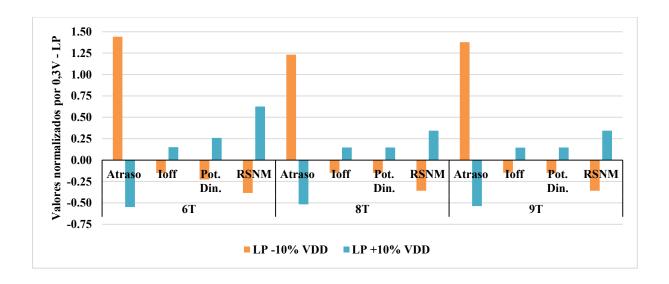

| Figura 5.5 Impacto da variabilidade de tensão na tecnologia LP                                        | 47   |

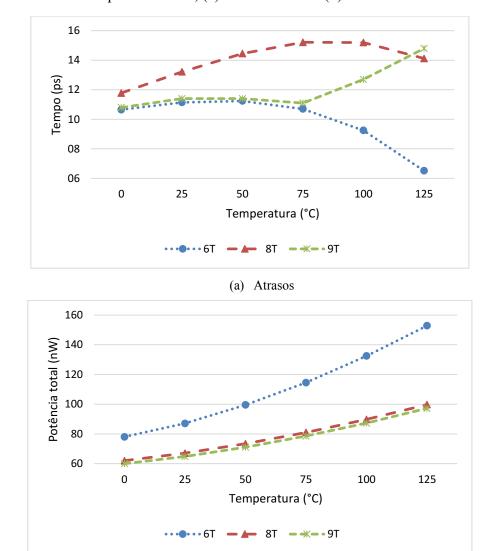

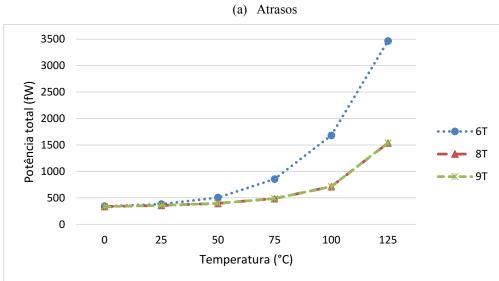

| Figura 5.6 Impacto da variabilidade de temperatura, tecnologia HP nos (a) atrasos, (b)    |    |

|-------------------------------------------------------------------------------------------|----|

| potência total, (c) corrente total e (d) RSNM                                             | 48 |

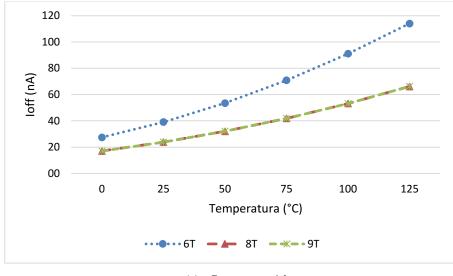

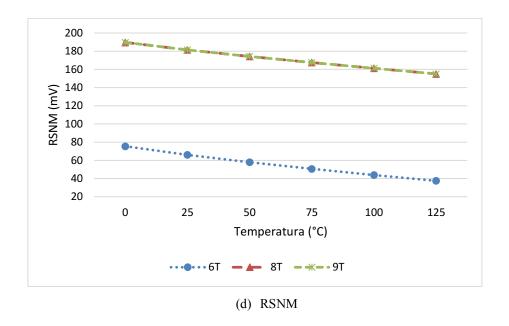

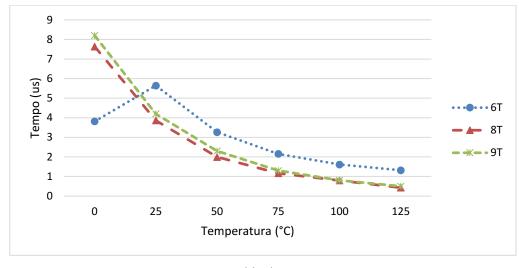

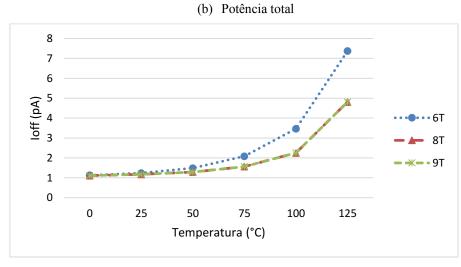

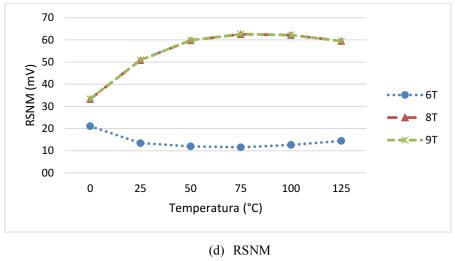

| Figura 5.7 Impacto da variabilidade de temperatura, tecnologia LP nos (a) atrasos, (b)    |    |

| potência total, (c) corrente total e (d) RSNM.                                            | 50 |

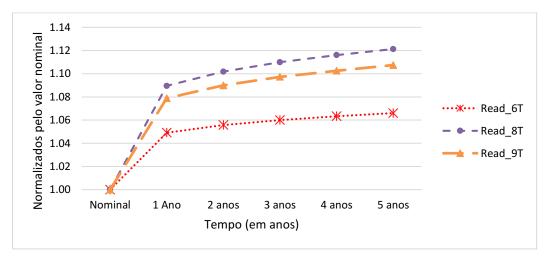

| Figura 5.8 Ação do envelhecimento por BTI (a) nos atrasos, (b) potência total e corrente  |    |

| estática na tecnologia HP                                                                 | 51 |

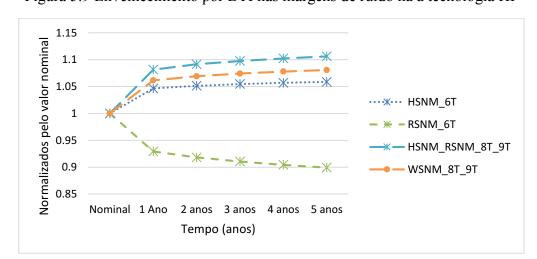

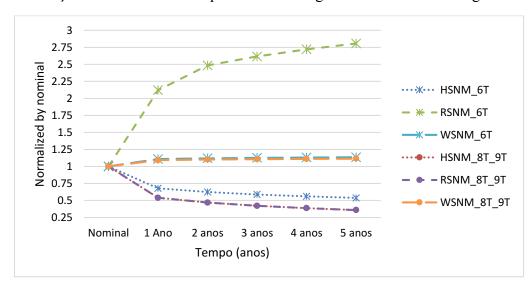

| Figura 5.9 Envelhecimento por BTI nas margens de ruído na a tecnologia HP                 | 52 |

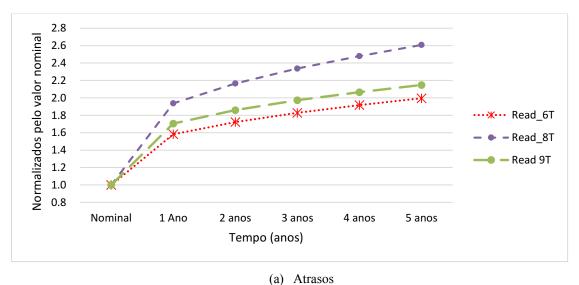

| Figura 5.10 Ação do envelhecimento por BTI (a) nos atrasos, (b) potência total e corrente |    |

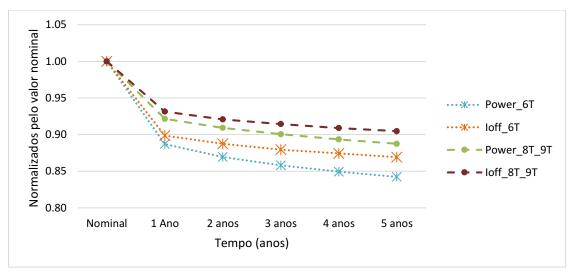

| estática na tecnologia LP                                                                 | 53 |

| Figura 5.11 Ação do envelhecimento por BTI nas margens de ruído na tecnologia LP.         | 54 |

# LISTA DE TABELAS

| Tabela 3.1 Resumo da abordagem realizada nos trabalhos citados | 29 |  |

|----------------------------------------------------------------|----|--|

| Tabela 4.1 Dimensionamento das células SRAM                    | 33 |  |

| Tabela 5.1 Resultados em condição nominal, tecnologia HP       | 42 |  |

| Tabela 5.2 Resultados em condição nominal, tecnologia LP       | 43 |  |

| Tabela 5.3 Impacto da variabilidade de processo, tecnologia HP | 44 |  |

| Tabela 5.4 Impacto da variabilidade de processo, tecnologia LP | 45 |  |

#### LISTA DE ABREVIATURAS E SIGLAS

BL Bitline

BLB Complementary Bitline

BTI Bias Temperature Instability

CMOS Complementary Metal Oxide Semiconductor

CR Cell-Ratio

LER Line-Edge Roughness

LET Linear Energy Transfer

NBTI Negative Bias Temperature Instability

NMOS Negative Metal Oxide Semiconductor

PBTI Positive Bias Temperature Instability

PMOS Positive Metal Oxide Semiconductor

PR Pull-up Rate

PVT Process, Variability, Temperature

RDF Random Dopant Fluctuations

RTN Random Telegraph Noise

SEE Single-Event Effects

SEU Single-Event Upset

SoC System on Chip

VLSI Very-Large-Scale Integration

# **SUMÁRIO**

| 1 IN          | TRODUÇÃO                                                           | 11         |

|---------------|--------------------------------------------------------------------|------------|

| 2 DE          | SAFIOS EM TECNOLOGIAS NANOMÉTRICAS                                 | 14         |

| 2.1 Va        | riabilidade PVT                                                    | 15         |

| 2.2 En        | velhecimento por BTI                                               | 17         |

| 2.3 Ou        | tros efeitos relevantes                                            | 18         |

| 3 PR          | OJETO DE MEMÓRIAS SRAM                                             | 20         |

| 4 MI          | ETODOLOGIA                                                         | 30         |

| 4.1 Me        | todologia de avaliação dos efeitos na tecnologia de 16nm           | 32         |

| 4.1.1         | Características de implementação das células 6T, 8T e 9T           | 32         |

| 4.1.2         |                                                                    | 33         |

| 4.1.3         |                                                                    | 34         |

| 4.1.4         |                                                                    | 36         |

| 4.1.5         |                                                                    | 37         |

| 4.1.6         | Experimentos para avaliação de efeitos de envelhecimento           | 38         |

| 5 RE          | SULTADOS                                                           | 39         |

| 5.1 Imj<br>39 | pacto da variabilidade,radiação e envelhecimento em tecnologias na | nométricas |

| 5.2 Co        | mparação da robustez a variabilidade e envelhecimento              | 42         |

| 6 CO          | ONCLUSÕES                                                          | 56         |

| 7 RE          | FERÊNCIAS                                                          | 58         |

| AN            | IEXOS                                                              | 63         |

#### **RESUMO**

Sistemas computacionais necessitam armazenar dados com desempenho adequado. Para alcançar este objetivo é necessário a utilização de uma hierarquia de memória, para combinar o uso de memórias de alta velocidade com memórias de alta capacidade e baixo custo por *bit*. Este trabalho é focado no estudo de memórias SRAM (*Static Random Access Memory*), que estão localizadas no topo da hierarquia de memória, que permitem o acesso aos dados em alta velocidade por serem fabricadas na mesma tecnologia do processador.

Memórias SRAM permitem o armazenamento de dados enquanto o sistema estiver conectado a alimentação. Este tipo de memória é projetado em estruturas de blocos, que por sua vez são um conjunto de colunas que conectam *n* células aos circuitos de escrita, leitura e précarga. A célula é o componente que armazena dados, sendo que cada uma armazena 1 *bit*.

A evolução tecnológica possibilitou a redução dos transistores e consequentemente aumentou o seu desempenho assim como reduziu a potência destes dispositivos. Na atual geração de circuitos integrados, as dimensões dos transistores chegaram à escala nanométrica. Entretanto, circuitos nessa escala são mais vulneráveis aos efeitos de variabilidade PVT (*Process Voltage Temperature*) e envelhecimento por BTI (*Bias Temperature Instability*). Estes efeitos fazem com que o circuito possa apresentar desvios em relação ao projeto inicialmente definido. Em células de memória SRAM, esses efeitos podem provocar a inversão dos *bits* armazenados, mau funcionamento e até mesmo impossibilitar a escrita e/ou leitura de dados.

Este trabalho tem como objetivo o estudo de três topologias de células de memória SRAM: 6T, 8T e 9T. É investigado o impacto da variabilidade PVT e envelhecimento por BTI no desempenho, robustez e consumo elétrico nas células avaliadas em duas tecnologias: 16n de alto desempenho em tensão nominal e *low power* em regime *near-threshold*.

Os resultados mostram que as células SRAM operando com tensão de alimentação reduzida são mais sensíveis a variabilidade de processo e envelhecimento. Considerando operação com tensão nominal e *near-threshold*, as células 8T e 9T se mostram mais robustas que a célula convencional 6T. No geral, a célula 8T mostrou menor variação diante dos impactos de variabilidade e envelhecimento. Embora a célula 9T apresente um comportamento próximo da 8T na maioria dos casos, justamente por ser uma adaptação da 8T, esta célula apresentou resultados de variabilidade PVT levemente inferior.

Palavras-chave: Células de memória, Nanotecnologia, SRAM.

#### **ABSTRACT**

Computing Systems need to store data with good performance. To achieve this goal is required to use a memory hierarchy to combine fast technologies with high number of bits and cheap cost per bit memories. This work is focused in SRAM memories that are made in the same technology of the processor which allows to have high performance.

SRAM (Static Random Access Memory) allows the data storage while the system is connected to the power supply. This kind of memory is organized in block structures that are formed by various columns with *n* cells connected in bitlines with write driver, read driver and precharge circuit. Each cell stores a single bit.

Technological evolution promoted transistors reducing and consequently increased its performance and reduced its power consumption. In modern integrated circuits, transistors sizing reached nanometric scale. However, circuits in that scale are more vulnerable to PVT variability, BTI aging and radiation by SEU. All these effects can make deviations in initial design expectation. In SRAM memory cells, it can provoke bit-flips, malfunctioning and even impede writing and/or reading data from memory.

This work objective is the evaluation of 1-bit SRAM cells 6T, 8T and 9T. The present work investigates the impact of PVT variability, BTI aging and SEU on performance, robustness, and power of evaluated cells in two technologies: 16n high performance at nominal voltage and low power at near-threshold regime.

Results show that SRAM cells at lower voltages show higher sensibility to variability and aging. Considering near-threshold and nominal operation 8T and 9T cells show higher tolerance to these effects than conventional 6T cell. In general, 8T cell showed smaller variation under variability and aging impact. Despite the 9T cell presented behavior close to 8T cell, precisely because it is an adaptation of 8T cell, this cell presents variability PVT results slight lower

# 1 INTRODUÇÃO

Atualmente, a sociedade está cercada de dispositivos que utilizam dispositivos computacionais para executar diversas tarefas, desde o controle das etapas de lavagem de máquinas de lavar roupas, temporizadores de microondas, controle de temperatura de geladeiras, até dispositivos como celulares e computadores. Para efetuar tais operações, são necessários circuitos que possuem a capacidade de armazenar e processar informações dentro de um determinado limite de tempo para cada aplicação. Para desempenhar esta função, são utilizados circuitos integrados, que possuem desempenho e consumo de energia adequados, aliados a um baixo valor de fabricação quando produzidos em larga escala. No decorrer das últimas décadas, estes circuitos foram miniaturizados, possibilitando o aumento de suas funcionalidades, aumento de desempenho e redução da potência por unidade de área e sem grande alteração no preço final do circuito.

A mininiaturização dos circuitos integrados possibilitou o auumento no desempenho de processamento, dessa forma, o tempo de execução dos dados passou a ser muito menor que o tempo de acesso à memória. Devido a isso, foi necessário aumentar a capacidade das memórias para compensar a diferença entre processamento e acesso (ROY; ISLAM, 2015). Segundo a lei de Nathan, os programas são como gás e se expandem até que ocupem todo um container (STALLINGS, 2012). Logo, o aumento da capacidade de armazenamento de dados e instruções se tornou uma necessidade tanto em questão de desempenho quanto em possibilidade de avanços a nível de *software*.

No projeto de um sistema de memória, a relação entre capacidade, desempenho e custo por *bit* é de difícil otimização, porque quanto maior o desempenho, maior o custo por *bit*, que acaba limitando a capacidade de *bits* da memória. Estes fatores são alguns dos mais importantes no projeto de uma tecnologia de memória. Para atingir uma boa relação entre estes fatores, é adotado o conceito de organização de memória em forma de hierarquia, aproveitando o melhor de cada tecnologia em cada nível. As memórias do topo da hierarquia são as mais rápidas, constituindo os registradores internos do sistema. Estas memórias apresentam alto custo por *bit*, o que limita a capacidade. A memória principal é utilizada para armazenar todos os processos em execução pelo sistema e deve ter uma relação entre desempenho, capacidade e custo por *bit* muito equilibrada. As memórias apresentadas na base da pirâmide possuem menor custo por *bit* o que possibilita a oferta de grande capacidade e são utilizados para armazenamento de dados e unidades de *backup*. As memórias para armazenamento em massa devem ter o menor

custo por *bit* possível para uma boa relação custo-capacidade. O equilíbrio na hierarquia é crucial para a obtenção de sistemas de alto desempenho e alta capacidade a um custo acessível.

Este trabalho é focado na análise de células de memórias SRAM (*Static Random Access Memory*), frequentemente utilizadas em memórias *cache*. Uma célula de memória SRAM é um arranjo de transistores que possibilita o armazenamento de um *bit* enquanto houver alimentação do circuito. Atualmente, este tipo de memória geralmente é fabricado no mesmo circuito integrado que o processador ou *System on Chip* (SoC), que possui todas as funcionalidades de um sistema computacional em um único *chip* e pode ser encontrado em circuitos que desempenham tarefas específicas e possuem demanda por alto desempenho ou baixo consumo de energia. Com a redução do tamanho dos transistores, a área de cada célula de memória SRAM reduziu, possibilitando o aumento da capacidade deste tipo de memória. Em circuitos VLSI (*Very Large-Scale Integration*) de alto desempenho, memórias SRAM podem ocupar mais de 70% da área total (SAMANDARI-RAD; HUGHEY, 2016).

Diante da evolução dos circuitos integrados e a contínua necessidade por armazenamento e desempenho, o estudo das células de memória SRAM é um fator de grande importância para a evolução dos sistemas computacionais. A célula utilizada irá definir a área total ocupada pela SRAM ou a densidade máxima de células em uma mesma área. A análise de células de memória inclui os seguintes aspectos: área, energia consumida, desempenho, robustez e efeitos das mais diversas fontes de variabilidade. As células devem ser projetadas de forma a satisfazerem as necessidades de cada projeto, ou seja, dependendo do projeto são necessárias células com menores atrasos, com menor consumo de energia ou uma combinação destes fatores. Assim, existe na literatura uma grande variedade de circuitos propostos para a SRAM. Dentre todas as diferentes propostas, a célula 6T (PAVLOV; SACHDEV; 2009) é a célula mais utilizada na indústria. Outras topologias observadas na literatura incluem a célula 8T (CHANG et al., 2005), a célula 10T Single Ended (CALHOUN; CHANDRAKASAN, 2007) e 10T Differential (CHANG et al., 2009) propostas para operar em circuitos com baixa tensão de alimentação, a célula 9T Half-Select-Free que reduz o problema das células que estão conectadas às bitlines sem realizar uma operação (SHIN; CHOI; PARK, 2017), a célula 4T Loadless (SANDEEP; DESHPANDE; ASWATHA, 2009) para a redução da área por célula e a célula 13T Radiation Hardened (ATIAS et al., 2016) para aplicações espaciais que necessitam de maior resistência a falhas de radiação. As células citadas são apenas uma pequena parcela das dezenas encontradas na literatura.

Uma célula de memória SRAM é considerada funcional quando ela consegue escrever, ler e armazenar um dado enquanto o circuito estiver em operação. Entretanto, a evolução da

tecnologia traz novos desafios que afetam o projeto de memórias SRAM. Dentre estes desafios, destacam-se os efeitos da variabilidade de processo, os efeitos de envelhecimento e o impacto provocado por colisões de partículas de radiação nos circuitos integrados nanométricos. Outro aspecto cada vez mais importante é considerar alternativas para a redução do consumo energético de memórias, por exemplo, explorando o comportamento das células operando na região de *near-threshold*. Assim, é necessário estimar o impacto destes fatores para obter-se memórias SRAM funcionais e dentro dos requerimentos especificados.

Neste contexto este trabalho destaca os efeitos da variabilidade e em células de memória SRAM projetadas em tecnologias nanométricas, demonstrando assim o problema a ser tratado, a metodologia adotada para avaliar estes efeitos e os resultados e conclusões obtidas através da aplicação das técnicas utilizadas. Este trabalho apresenta as análises realizadas para verificar o comportamento de células SRAM, observando o desempenho através dos: 1) tempos de escrita e leitura; 2) robustez utilizando as margens de ruído estático; e 3) a potência total e o consumo estático. Essas características serão avaliadas em circuitos de alto desempenho com tensão de alimentação nominal e circuitos *low power* com tensão *near-threshold*.

Deste modo, o objetivo final desta dissertação é: Avaliar dos efeitos de variabilidade e envelhecimento em células de memória SRAM em tecnologias nanométricas em circuitos de alto desempenho e *low power*. Dessa forma, identifica-se quais células apresentam características de desempenho, potência e robustez são mais apropriadas para cada tipo de projeto desejado.

O texto está organizado da seguinte forma: No Capítulo 1 foram contextualizados o objeto de estudo e seus desafios. O Capítulo 2 mostra o referencial teórico, apresentando os principais conceitos associados aos desafios de projeto de circuitos integrados em escala nanométrica, introduzindo os conceitos de variabilidade PVT e envelhecimento por BTI. O Capítulo 3 apresenta aspectos importantes relacionados ao projeto de memórias SRAM. O Capítulo 4 mostra a estrutura para a concepção deste trabalho e modelagem da variabilidade PVT e envelhecimento. O Capítulo 5 apresenta a análise dos resultados parcialmente obtidos. O Capítulo 6 traz a conclusão do trabalho desenvolvido, proposta de dissertação e cronograma para as próximas etapas.

## 2 DESAFIOS EM TECNOLOGIAS NANOMÉTRICAS

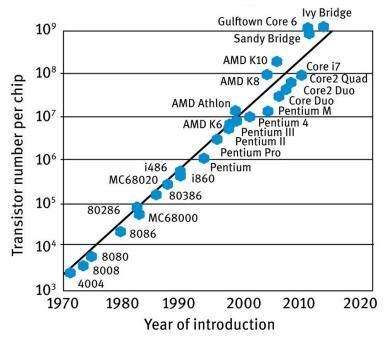

No decorrer das últimas décadas, as dimensões dos transistores em circuitos integrados VLSI vem sendo reduzida, chegando à escala nanométrica. A miniaturização do transistor possibilita o aumento da quantidade deles em uma mesma área, acrescentando novas funcionalidades e capacidade de armazenamento das memórias. Outro aspecto importante da miniaturização é o aumento do desempenho e a redução da energia consumida por cada dispositivo. Na Figura 2.1 é mostrada a evolução dos circuitos integrados em relação ao número total de transistores em diversos processadores. Em 1965, Gordon Moore projetou que era economicamente viável dobrar o número de transistores em um circuito integrado em 18 meses, sem aumentar o custo (MOORE, 1965). A previsão de Moore virou uma meta da indústria de semicondutores e passou a ser chamada de Lei de Moore, impulsionando a evolução dos dispositivos.

Figura 2.1 Lei de Moore

Fonte: KONIG; OSTENDORF, 2015.

A redução das dimensões dos transistores aumenta o desempenho e reduz a potência por dispositivo. Porém, essa redução traz novos desafios, incluindo o aumento do consumo estático devido à redução do canal do transistor, as margens de erro no processo de fabricação aumentam diante do tamanho da dimensão mínima dispositivo se aproximar cada vez mais ao tamanho de um átomo de silício. As dificuldades no processo de manufatura podem ocasionar em falhas permanentes nos dispositivos. Ao reduzir o tamanho do transistor a tensão de alimentação também é reduzida, isso torna o dispositivo mais sensível a falhas transientes. Outro aspecto

que se torna relevante é a redução do desempenho por ação do envelhecimento. A cada redução nas dimensões dos transistores, surgem novas incertezas quanto ao dispositivo que será impresso, dessa forma é necessário estimar todos esses fatores e possíveis consequências.

Neste Capítulo serão apresentados os principais conceitos relacionados aos efeitos da variabilidade processo, tensão e temperatura, os efeitos de envelhecimento provocados pelo efeito BTI (*Bias Temperature Instability*) e, por fim, outros efeitos relevantes.

#### 2.1 Variabilidade PVT

Com o alcance da escala nanométrica, a litografia passou a ser um grande desafio para a continuação da evolução dos circuitos integrados, uma vez que a largura de onda adotada no processo de litografia passou a ser maior que a escala de fabricação dos transistores (BERNSTEIN et al., 2006). Isto introduz variações geométricas que afetam as características elétricas dos dispositivos, mesmo quando fabricados em um mesmo *die*. Diante dos desafios de fabricação, os efeitos de variabilidade se tornaram um parâmetro importante a ser estimado no projeto de circuitos integrados nanométricos. Tecnologias abaixo de 65nm possuem precisões paramétricas exponencialmente mais difíceis devido à mecânica quântica (BERNSTEIN et al., 2006). Dessa forma, quanto menor o dispositivo, maior serão os efeitos da variabilidade.

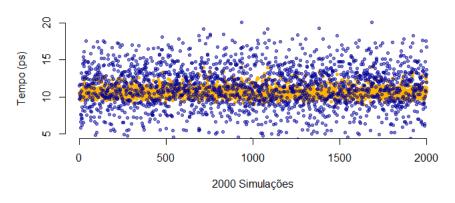

A variabilidade provoca alterações nas resistências e capacitâncias dos dispositivos, impactando principalmente a tensão de limiar dos transistores. Consequentemente, afeta os tempos de atrasos, consumo de energia e robustez de circuitos nanométricos. Devido à alta densidade de células SRAM, estas variações podem impactar diretamente o desempenho e consumo elétrico de todo o circuito. A Figura 2.22 apresenta um gráfico de dispersão ilustrando o impacto da variabilidade de processo nos tempos de escrita e leitura de uma célula SRAM 6T na tecnologia de 16nm em tensão nominal e tecnologia de alto desempenho. Neste exemplo, observa-se que os efeitos da variabilidade de processo podem se manifestar diferentemente para cada métrica observada, sendo neste caso o tempo de leitura, em azul na figura, o que apresenta maior dispersão no decorrer de 2000 simulações.

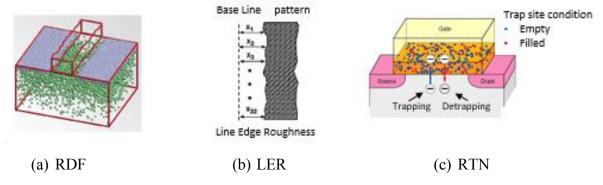

A principal fonte de variabilidade em circuitos em escala nanométrica é a de processo. Os principais fatores que provocam a variabilidade de processo são: *Random Dopant Fluctuations* (RDF), *Line Edge Roughness* (LER) e *Random Telegraph Noise* (RTN), ilustradas na Figura 2.33. A RDF ocorre devido a diferença no número de portadores de carga no transistor como ilustra a Figura 2.03 (a). Em transistores com dimensões reduzidas, há um número menor de portadores de carga e a diferença no número total de portadores se torna mais significativa

entre circuitos em uma mesma tecnologia de fabricação. A RDF é a fonte principal de variação na tensão de limiar (LI et al., 2010).

Figura 2.2 Dispersão dos tempos de escrita (pontos amarelos) e leitura (pontos azuis) diante dos efeitos da variabilidade

Fonte: Os autores.

Figura 2.3 Efeitos que influenciam nas características elétricas dos dispositivos

Fonte: ABU-RAHMA et al., 2013.

A LER ocorre devido a imperfeição geométrica nas bordas do *gate*, como ilustra a Figura 2.3 (b). Como o *gate* controla a passagem de corrente pelo transistor, essas alterações afetam o campo elétrico do dispositivo, impactando a tensão de *threshold* e a corrente máxima. A RTN ocorre devido a imperfeições no óxido que isola o *gate* do canal, como ilustra a Figura 2.32 (c). Estas imperfeições criam armadilhas nas quais os portadores ficam presos durante a passagem de corrente afetando a quantidade de portadores que passam pelo canal e alterações no campo elétrico entre o *gate* e o canal. Em (KARAPETYAN; SCHLICHTMANN, 2017) é avaliado o impacto da variabilidade de processo em células SRAM utilizando transistores FinFET. A variabilidade de processo em circuito com baixa tensão de alimentação é avaliada em (SAMANDARI-RAD; HUGHEY, 2016).

A fabricação de circuitos em escala nanométrica afeta tanto os dispositivos quanto as interconexões entre eles. Variações na espessura do metal que conecta diferentes dispositivos afeta a resistência e consequentemente pode ser um dos fatores que impacta em variações na

tensão e temperatura do circuito. Estas variações afetam diretamente a corrente de saturação e consequentemente o desempenho e o consumo de energia de cada dispositivo, além da potência associada à resistência elétrica das interconexões. A Figura 2.44 ilustra como a temperatura pode se distribuir em um circuito integrado. A temperatura pode ser diferente entre os blocos de memória SRAM, provocando diferenças no desempenho, potência e robustez entre células de memória de diferentes blocos. Em (YABUUCHI et al., 2007) e (ISLAM; HASAN, 2012) são estimados os efeitos de variações de temperatura em SRAMs, além de propor técnicas para avaliar e reduzir o seu impacto.

Figura 2.4 Variações de temperatura em um circuito integrado

Fonte: ABU-RAHMA et al., 2013.

A redução da tensão dos circuitos, aliado a variações de espessura das vias de metal pode produzir variações na tensão que chega aos circuitos. Estas variações provocam alterações principalmente nos atrasos e consumo de potência dos circuitos (ALMEIDA et al., 2018). Dependendo da variação, pode gerar alterações que fazem com que o circuito tenha desempenho ou consumo de energia diferentes das necessidades de determinado projeto. Este tipo de variação mais a variabilidade de processo e temperatura é conhecido como variabilidade PVT (*Process, Voltage and Temperature*). Em (ISLAM; HASAN, 2012) é feito um estudo deste tipo de análise em células SRAM e seu impacto nas características relacionadas ao consumo de energia e robustez.

#### 2.2 Envelhecimento por BTI

Com a redução do transistor, a camada de óxido entre o *gate* e o canal também é reduzida. O uso do transistor faz com que o campo elétrico do óxido aumente gradualmente. Isso faz com que ocorra uma degradação do dispositivo devido ao seu envelhecimento. A degradação ocorre devido aos efeitos de *Bias Temperature Instability* (BTI) e afeta diretamente o tempo de vida útil do dispositivo. Quando o BTI ocorre em dispositivos PMOS é chamado de NBTI e em dispositivos NMOS é chamado de PBTI. Ambos causam o aumento da tensão de

limiar dos transistores (JIN et al., 2018) e consequentemente a redução do desempenho do dispositivo.

O BTI ocorre devido ao estresse causado nos transistores quando estão conduzindo, ou seja, quando a tensão no *gate* do transistor NMOS está em '1' e a tensão do gate do PMOS está em '0'. Quando o transistor não está conduzindo, ele passa para a fase de recuperação (BUTZEN et al., 2013). A Figura 2.55 ilustra a variação da tensão de limiar V<sub>th</sub> no decorrer do tempo, variando entre fases de estresse e recuperação de um transistor. Porém, a fase de recuperação causa uma recuperação parcial e o uso contínuo faz com que a tensão de limiar aumente, degradando o dispositivo. O aumento da tensão de limiar impacta diretamente o seu desempenho, que reduz com o passar do tempo.

V<sub>th</sub>

SRSRSRSRS

1 Clock Cycle time

Figura 2.5 Efeitos de BTI na tensão de limiar do transistor

Fonte: HU et al., 2016.

Em célula de memória SRAM os efeitos de BTI podem provocar alterações na robustez da célula de memória. Os transistores que compõem os inversores internos da célula tendem a permanecerem ativados por muito mais tempo que os transistores de passagem. Desta forma, a principal consequência do envelhecimento em células SRAM é a redução da robustez de leitura pelo fato dos transistores da rede *pull-down* dos inversores ficarem mais lentos que os transistores de passagem.

## 2.3 Outros efeitos relevantes

A avaliação de circuitos em escala nanométrica deve considerar outros efeitos além dos já apontados. Um aspecto relevante no projeto de circuitos integrados é o consumo elétrico do circuito. A redução do canal dos transistores aumentou o consumo estático, que ocorre devido a corrente de fuga, esta característica indesejável causa o consumo elétrico de dispositivos que idealmente não deveriam permitir a passagem de corrente elétrica (ROY; MUKHOPADHYAY; MAHMOODI-MEIMAND, 2003). Em células de memória, o consumo estático é um grave problema devido a sua densidade nos circuitos integrados atuais.

Além disso, aplicações portáteis necessitam de memórias com menor potência (SAMANDARI-RAD; HUGHEY, 2016), para aumentar a autonomia do dispositivo sem a necessidade de carregar a todo momento. Para estes casos, uma das opções é aplicar a técnica de *voltage scaling*, que consiste em reduzir a tensão de alimentação abaixo da tensão nominal de determinada tecnologia. Entretanto, a redução da tensão de memórias SRAM reduz também o desempenho de forma exponencial (ALMEIDA; BUTZEN; MEINHARDT, 2016).

Circuitos de memória que operam na região *near-threshold* tem sua operação limitada devido aos efeitos da variabilidade (KULKARNI; KIM; ROY; 2007). Nesta região, a tendência é haver maiores variações dos valores médios em relação ao nominal de suas características. Dessa forma, o impacto em células de memória que operam na região *near-threshold*, além de afetar o desempenho, consumo elétrico e a robustez, pode impedir que a célula de memória funcione adequadamente.

Além das falhas transientes devido à radiação, células de memória também precisam considerar outros tipos de falhas. Em tecnologias nanométricas, passaram a ser mais frequentes em circuitos atuais a ocorrência de falhas do tipo *resistive bridge*, decorrentes de um caminho resistivo indesejado entre os nodos dos circuitos, e *resistive open*, decorrentes do efeito resistivo devido a imperfeições na criação das vias (MARTINS, 2016). Também são relevantes os efeitos de falhas que podem comprometer o funcionamento de um circuito de forma permanente, por exemplo, de falhas *stuck-open*, que faz com que o transistor fíque permanentemente aberto, e *stuck-on*, no qual o transistor fica permanentemente fechado (WADSACK, 1978). Em células de memória, falhas *stuck-on* e *stuck-open* podem fazer que uma célula fíque permanentemente armazenando um valor fixo, ou que o valor seja modificado durante um processo de leitura (MARQUES et al., 2018).

Dessa forma, verifica-se a necessidade de analisar os impactos de feitos de variabilidade e envelhecimento em tecnologias nanométricas. Como o tempo de acesso da memória é muito maior que o tempo de processamento de dados, uma memória com desvios em seu desempenho pode impactar no desempenho de todo o sistema. Em relação à potência, diante da densidade de células por área e o seu número total em um circuito integrado, sua variação pode trazer impactos diretamente no consumo total do sistema e na dissipação de calor em circuitos de alto desepenho. A robustez se torna um problema em SRAMs projetadas com baixa tensão de operação e pode gerar células defeituosas. Portanto, todos os efeitos abordados nesta seção interferem diretamente na funcionalidade tanto da memória SRAM quanto no sistema como um todo.

#### 3 PROJETO DE MEMÓRIAS SRAM

Nesta seção serão abordadas as principais características de células SRAM, mostrando o seu funcionamento, organização e um compilado de células de memória para diferentes tipos de aplicações.

## 3.1 Organização da SRAM

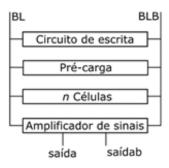

A memória SRAM consiste em um dispositivo no qual os dados e instruções são armazenados em células de memória dispostas em palavras de *n bits*. Para garantir o correto funcionamento da memória, existe um conjunto de sinais de controle, destacando-se os sinais de habilitação de leitura ou escrita. Memórias SRAM são organizadas em *m* blocos de células de memória, com a menor área possível para otimizar sua capacidade total. A Figura 3.1 apresenta um modelo simplificado de como é organizado um bloco de células de memória. Cada linha pode conter uma ou mais palavras de memória. As colunas contêm diversas células de palavras diferentes, porém elas só podem ser acessadas para escrita ou leitura individualmente. As colunas podem ser utilizadas para a leitura em paralelo dos *bits* de uma palavra. Em cada bloco há circuitos decodificadores de linha e coluna que possibilitam o acesso apenas do *bit* ou palavra desejada.

Célula ŧ Célula Célula Célula Decodificador de coluna **↑** Endereço

Figura 3.1 Bloco de células SRAM

Fonte: Os autores.

Blocos de memória SRAM são compostos por colunas que costumam conter entre 64 e 256 células de memória (PAVLOV; SACHDEV, 2009). A Figura 3.2 apresenta o uma coluna contendo os circuitos básicos para o acesso e armazenamento de dados. Ela é composta pelos circuitos de escrita, pré-carga e amplificador de sinais, que possibilita a leitura de um valor previamente armazenado, além de um número n de células. Todos esses circuitos são

conectados entre si através das *bitlines BL* e *BLB*, que possibilitam a interação entre os circuitos para a escrita ou leitura de dados em determinada célula. O número de células e circuitos que compõem uma coluna pode variar diante das definições de *projeto* e das células utilizadas.

Memórias SRAM armazenam dados em estruturas chamadas células de memória. Cada célula geralmente armazena 1 *bit*, dessa forma podem ser necessárias milhões dessas estruturas em um circuito integrado moderno. Estas células precisam ser pequenas, ter alto desempenho e boa robustez, que é a capacidade de manter os *bits* armazenados de forma que não haja perda de informação. Células de memória possuem três estados: *hold* (manutenção do *bit* armazenado), escrita e leitura.

Figura 3.2 Estrutura básica de uma coluna de células.

Fonte: Os autores.

#### 3.2 Célula 6T

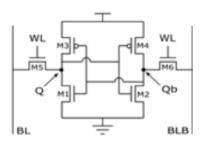

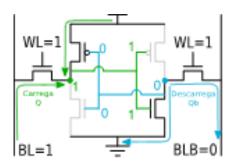

A célula mais utilizada na indústria é a 6T (PAVLOV; SACHDEV, 2009) ilustrada na Figura 3.3. Devido a necessidade por uma memória de alta capacidade, a área é o principal fator para a escolha de uma célula. Até então, a célula 6T consegue melhor relação entre área, desempenho, consumo elétrico e estabilidade. Esta célula é composta por seis transistores, quatro deles compõem dois inversores CMOS (*M1-M3* e *M2-M4*) e os outros dois são utilizados como transistores de passagem (*M5* e *M6*). O conteúdo é armazenado no nodo *Q*, que é acessado pela *bitline BL* através do transistor de passagem *M5*. Em *Qb* é armazenado o complemento lógico de *Q*, acessado pela *bitline BLB* através do transistor *M6*. O sinal *wordline* (*WL*) habilita o acesso à célula para os processos de escrita ou leitura. No caso de acesso de uma palavra de memória, a *wordline* pode permitir acesso a várias colunas simultaneamente, possibilitando o acesso de todos os bits de uma palavra de forma paralela.

Figura 3.3 Diagrama elétrico da célula 6T

Fonte: PAVLOV; SACHDEV, 2009

O processo de escrita de um valor em uma célula necessita de um circuito de escrita, que possibilita a gravação do *bit* desejado. A escrita ocorre ao aplicar a tensão correspondente ao nível lógico do *bit* a ser escrito na *bitline BL*, e seu complemento lógico em *BLB*. Após, a célula desejada é acessada através da sua *wordline*. A tensão aplicada em *BL* força o nodo *Q* a assumir esse valor enquanto que *BLB* força o nodo *Qb*, como exemplificado na Figura 3.4. Assim que a célula estiver com o seu valor gravado, a *wordline* deve ser desativada. A retroalimentação dos inversores CMOS garantem a manutenção do valor até que seja sobrescrito ou que seja interrompida a alimentação dos inversores.

Figura 3.4 Escrita do valor '1' na célula 6T

Fonte: Os autores.

A leitura de um valor armazenado em uma célula de memória 6T, assim como em outras células que não possuam uma *bitline* exclusiva para a leitura, depende de dois circuitos: précarga e amplificador diferencial. A pré-carga mantém *BL* e *BLB* pré-carregadas enquanto todas as células estão em *hold*. Para realizar a leitura, as *bitlines* devem estar pré-carregadas e equalizadas. Depois, é necessário habilitar o acesso à célula desejada através de sua *wordline*. O nodo que estiver armazenando o valor '0' irá descarregar parte da tensão da *bitline* conectada a ele, enquanto que a outra *bitline* mantém sua tensão em '1', como ilustra a Figura 3.5. Quando houver a diferença de tensão necessária entre as *bitlines*, a *wordline* da célula é desativada e o

amplificador de sinais é ativado. O amplificador de sinais recebe a tensão das *bitlines* e força a *bitline* que foi parcialmente descarregada a descarregar completamente, enquanto que a que possui tensão maior se mantem carregada. Dessa forma, ele verifica qual valor estava armazenado em cada nodo da célula de memória e fornece o valor referente ao nodo *Q*.

WL=1 WL=1

Figura 3.5 Leitura do valor '1' na célula 6T

Fonte: Os autores.

Um fator muito importante no projeto de células SRAM é o dimensionamento dos transistores e sua influência no desempenho e estabilidade. Em uma célula convencional 6T, o dimensionamento pode ser efetuado observando os parâmetros CR (*Cell Ratio*) e PR (*Pull-Up Ratio*) (RABAEY; CHANDRAKASAN; NIKOLIC, 2003). CR é a relação entre os transistores da rede *pull-down* e os transistores de passagem, enquanto que PR é a relação entre os transistores da rede *pull-up* e os transistores de passagem. O valor de CR é definido como  $CR = W_{MI}/W_{MS}$ , esta relação impacta principalmente na estabilidade e desempenho de leitura. Para manter a célula robusta e evitar que o *bit* armazenado seja corrompido, CR deve ser maior ou igual a 1. O valor de PR é definido como  $PR = W_{M3}/W_{MS}$  e têm influência na estabilidade e desempenho de escrita e preferencialmente deve ser igual ou menor que 1, para minimizar a área total da célula de memória.

#### 3.3 Células SRAM para aplicações específicas

Novas células vêm sendo propostas nos últimos anos, principalmente devido a necessidade de memórias com menor consumo para aplicações que utilizam baterias como fonte de alimentação ou maior resistência à variabilidade, envelhecimento e outros fatores relacionados à escala nanométrica.

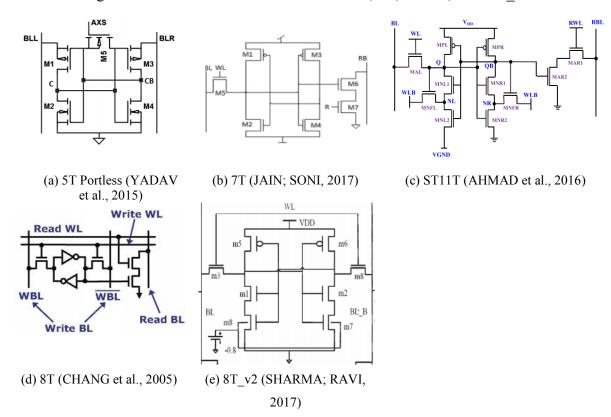

A célula 5T *Portless* (YADAV et al., 2015) apresentada na Figura 3.6 (a) é uma alternativa para a redução de área para circuitos de alto desempenho. A célula 7T proposta por (JAIN; SONI, 2017) apresentada na Figura 3.6 (b) foca a redução do consumo total, reduzindo

a potência média durante os processos de leitura e escrita. A célula *Single-Ended Schmitt-Trigger-Based* (AHMAD et al., 2016) mostrada na Figura 3.6 (c) é uma proposta que utiliza a técnica de inversores *Schmitt-Trigger* para reduzir a potência, consumo estático e melhorar as margens de ruído de escrita e leitura. A célula 8T (CHANG et al., 2005) apresentada na Figura 3.6 (d) é uma das mais encontradas na literatura após a 6T, sendo amplamente usada como ponto de comparação para células que operam com baixas tensões de alimentação. Uma pequena modificação na célula 8T\_v2 é proposta em (SHARMA; RAVI, 2017) e promete operar em circuitos *low power* com a maior estabilidade entre as células encontradas na literatura e redução de 66% da potência em relação à célula 8T proposta em (CHANG et al. 2005), seu diagrama elétrico é representado na Figura 3.6 (e).

O impacto da variabilidade PVT em memórias SRAM é avaliado em diversos trabalhos, principalmente em relação à variabilidade de processo. Em (TORRENS et al., 2017) é feito um estudo da relação do dimensionamento mínimo da célula 6T e seu impacto na área, potência, desempenho e estabilidade. O estudo inclui o impacto da variabilidade de processo em células de área mínima. Outro trabalho que relaciona área e impacto da variabilidade é observado em (KARAPETYAN; SCHLICHTMANN, 2017), avaliando este impacto nas margens de ruído, capacidade de descarga das *bitlines* e corrente estática, porém em uma célula 6T projetada com transistores FinFET.

Figura 3.6 – Células de memória 5T Portless, 7T, ST11T, 8T e 8T v2.

Em (KIM; LEE; DO, 2018) é proposta uma célula 9T\_v1 com operação na região *near-threshold*, com baixo consumo por acesso e propõe ser robusta a variações PVT, seu diagrama elétrico é apresentado na Figura 3.7. Dadas suas características de baixo consumo em operação NT e por ser proposta para mitigar variabilidade de processo, esta célula é um dos circuitos avaliados neste trabalho e comparado com o funcionamento da células 6T tradicional e 8T da Figura 3.6 (d). A célula *Power-Gated* 9T é apresentada na Figura 3.7 (b) propõe imunidade a *soft erros* e possui apenas uma *bitline* tanto para escrita quanto para a leitura e um mecanismo para evitar descargas desnecessárias de um dos seus nodos (OH et al., 2017). Em (DINESHKUMAR; DEVI, 2017) é proposta uma célula 9T, apresentada na Figura 3.7 (c) tolerante a variações de processo em aplicações *low power*, mas que pode operar em circuitos com tensão nominal reduzindo o consumo de energia em até 91% em relação às células 6T e a 8T proposta por (CHANG et. al, 2005).

Células projetadas para operar em *low power* tendem a criar um mecanismo de leitura que acessa o *bit* armazenado de forma indireta, tentando não causar interferência das *bitlines* sobre os nodos que armazenam os *bits*. Em circuitos que operam em baixas tensões, o tempo de leitura é maior. Caso ocorra um distúrbio em uma das *bitlines* durante a leitura, pode ocorrer a inversão do bit armazenado. Enquanto que em células que possuem este mecanismo, o valor se mantém inalterado.

Figura 3.7 – Células SRAM 9T\_v1, PG9T e 9T\_v2.

A avaliação dos efeitos de envelhecimento por BTI é observado em diversos trabalhos, nos quais possuem diversas metodologias distintas, mas com resultados próximos. Em (LEE et al., 2017) são avaliados os efeitos de BTI nas margens de ruído de SRAMs projetadas em tecnologia CMOS 20nm e FinFET 20nm, propondo um novo modelo para estimar o envelhecimento. Em (AHMAD; ALAM; HASAN, 2017) são propostas duas células, 11T\_v1 apresentada na Figura 3.8 (a) e a 11T v2 na Figura 3.8 (b), que reduzem os distúrbios no

processo de leitura, estas células são avaliadas diante do impacto de BTI. No trabalho realizado por (JIN et al., 2018) é feita a verificação das características e comportamento de BTI na SRAM projetadas na tecnologia FinFET 10nm, observando as variações nas margens de ruído da célula SRAM.

Em projetos que operam em situações críticas de robustez, são necessários circuitos auxiliares e técnicas de projeto para garantir o funcionamento das memórias SRAM. Em (ASYAEI; EBRAHIMI, 2018) é proposto um circuito auxiliar para variar a tensão das *bitlines* dinâmicamente para reduzir a potência dissipada, principalmente no estado de *hold*. Em (CHANG et al., 2017) é proposta uma técnica de acesso à célula 6T que utiliza dois sinais de *wordline*, sendo um para cada transistor de passagem e dois sinais terra para os transistores da rede *pull-down*, permitindo a operação com tensões de alimentação abaixo do observado em células 6T projetadas do modo convencional. O impacto da relação entre largura e comprimento dos transistores que compõem a célula 6T, variação da tensão de limiar, leiaute e tensão aplicada nas *wordlines* é avaliado em (GOYAL; TOMAR; GOYAL, 2017). Em (POMPL et al., 2015) é proposta uma técnica para estimar a tensão mínima de operação para células de memória. Técnicas de redução de potência de SRAMs são propostas em (SAMANDARI-RAD; HUGHEY, 2016), considerando o impacto da variabilidade sobre estas técnicas.

Figura 3.8 Células SRAM 11T v1 e 11T v2.

Memórias SRAM são utilizadas para diversas finalidades, sendo que em alguns casos são necessários projetos específicos para atender aos requerimentos de projeto. A compressão de vídeo possui alto consumo de energia, em (KIM; CHANG; LEE, 2018) é proposto um projeto que utiliza células de memória com dimensionamento de acordo com a relevância do

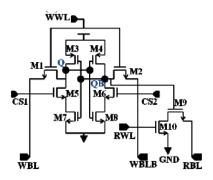

dado na compactação de vídeo. Os dados mais importantes são armazenados em células maiores e mais robustas, enquanto que os dados que não são críticos são armazenados em células menores, reduzindo a área potência. SRAMs podem ser utilizadas em LUTs (*LookUp Table*) de placas FPGA (*Field Programmable Gate Arrays*), a célula PFC 10T (SINGH et al., 2018) foi projetada para melhorar a estabilidade de escrita e leitura e corrente estática em relação às células 6T e 8T (CHANG et al., 2005) em LUTs.

Atualmente, dispositivos FinFET já são fabricados e podem ser utilizados para a concepção de memórias SRAM. Em (ENSAN; MOAIYERI; HESSABI, 2018) é proposta uma célula 11T utilizando FinFETs para operar em near-threshold, propondo maior estabilidade e desempenho de escrita e leitura mesmo em dispositivos com dimensionamento mínimo. Em (PAHUJAA et al., 2017) é proposta uma célula 9T utilizando FinFETs para circuitos *low power*, esta célula foi proposta para alta estabilidade de leitura e escrita mesmo sob a ação de variações de processo e temperatura. Outra proposta que utilizada FinFETs é observada em (LIMACHIA et al., 2017), porém esta é voltada para circuitos de alto desempenho, mas propondo a redução da potência em relação a outras propostas, além de aumentar a RSNM em relação à célula 6T, além de propor alta resistência à variabilidade de processo.

Figura 3.9 Células SRAM PFC 10T, 9T v3, 9T v4 e 10T.

(a) PFC 10T (SINGH et al, 2018)

(b) 9T\_v3 (ENSAN; MOAIYERI; HESSABI, 2018)

(c) 9T\_v4 (PAHUJAA et al., 2017)

(d) 10T (LIMACHIA et al., 2017)

Para lidar com os problemas encontrados atualmente e novos desafios provenientes da miniaturização, novos tipos de técnicas de projeto de memórias e novos dispositivos vêm sendo propostos. Em (PENG et al., 2017) é proposta uma célula 7T1R não-volátil, que adiciona um resistor que possibilita o armazenamento do dado mesmo sem o circuito estar alimentado, projetado para operar principalmente em circuitos *low power*, mantendo boa robustez. Dispositivos TFET (*Tunnel Field-Effect Transistor*) foram testados em (ANJU et al., 2017) propondo uma memória SRAM de boa eficiência energética em circuitos voltados à IoT (*Internet of Things*), além de maior resistência aos efeitos da variabilidade. Em (TAYAL; NANDI, 2017) é feita uma análise do desempenho e robustez de SRAMs utilizando dispositivos JLSiNTFET (*Junctionless Silicon Nanotube Field-Effect Transistor*), mostrando resultados promissores, principalmente em relação à robustez.

Na Tabela 3.1 é apresentado um resumo do tipo de análise ou proposta em vários dos trabalhos citados. Estes trabalhos foram selecionados de acordo com a relevância com o tipo de análise e foco do presente trabalho. A tabela aponta as principais características de análise e de cada proposta. Vários trabalhos propõem novas células, técnicas e/ou circuitos auxiliares, metodologia para análise das células, enquanto que outros analisam propostas e tecnologias já existentes, verificando e testando com as mais variadas abordagens, como as questões de variabilidade, envelhecimento e operação *low power*. É importante destacar que além dos trabalhos citados, há outros tipos de propostas e análises, porém estes diferem do objeto de estudo desse trabalho de avaliar células mais robustas aos efeitos de variabilidade.

É interessante ressaltar que nos últimos anos várias novas células estão sendo propostas na literatura. A análise da variabilidade é presente em grande parte dos trabalhos, muitos destes avaliando o comportamento de células SRAM projetadas em simuladores 3D, como a ferramenta TCAD, ou em protótipos de circuitos em tecnologias atuais. Poucos trabalhos abordam os efeitos de envelhecimento. A maioria dos trabalhos atuais reforça a importância de reduzir o consumo de energia do sistema de memória, explorando técnicas e circuitos para operação em baixa potência. Dentre a analise, nenhum trabalho estudado apresentou conjuntamente a avaliação de circuitos quanto ao envelhecimento e variabilidade, considerando operação nominal e operação neart-threshold como esta proposta apresenta.

#### 3.4 Comparação entre os trabalhos citados

Tabela 3.1 Resumo da abordagem realizada nos trabalhos citados.

| Trabalho                        | Proposta<br>de nova<br>célula | Nova<br>técnica<br>ou circuito<br>auxiliar | Nova<br>metodologia<br>de análise | Análise de variabilidade | Análise de envelhecimento | Low<br>power |

|---------------------------------|-------------------------------|--------------------------------------------|-----------------------------------|--------------------------|---------------------------|--------------|

| SAMANDARI-RAD;<br>HUGHEY, 2016  |                               | X                                          |                                   |                          |                           | X            |

| ISLAM; HASAN,<br>2012           |                               |                                            | x                                 | х                        |                           |              |

| KARAPETYAN;<br>SCHLICHTM., 2017 |                               |                                            | x                                 | x                        |                           |              |

| YADAVet al., 2015               | X                             |                                            |                                   |                          |                           |              |

| JAIN; SONI, 2017                | X                             |                                            |                                   |                          |                           |              |

| AHMAD et al., 2016              | X                             |                                            |                                   |                          |                           | X            |

| SHARMA; RAVI,<br>2017           | х                             |                                            |                                   |                          |                           | x            |

| TORRENS et al.,<br>2017         |                               |                                            | x                                 | x                        |                           |              |

| KIM; LEE; DO, 2018              | X                             |                                            |                                   | X                        |                           | X            |

| OH et al., 2017                 | X                             |                                            |                                   | X                        |                           |              |

| DINESHKUMAR;<br>DEVI, 2017      | Х                             |                                            |                                   | х                        |                           | х            |

| LEE et al., 2017                |                               |                                            | X                                 |                          | X                         |              |

| AHMAD; ALAM;<br>HASAN, 2017     | х                             |                                            |                                   |                          | Х                         |              |

| JIN et al., 2018                |                               |                                            | X                                 |                          | X                         |              |

| ASYAEI;                         |                               |                                            |                                   |                          |                           |              |

| EBRAHIMI, 2018                  |                               | X                                          |                                   |                          |                           | X            |

| CHANG et al., 2017              |                               | Х                                          |                                   |                          |                           | X            |

| GOYAL; TOMAR;                   |                               |                                            |                                   |                          |                           |              |

| GOYAL, 2017                     |                               |                                            | X                                 |                          |                           |              |

| POMPL et al., 2015              |                               | X                                          | X                                 |                          |                           | X            |

| KIM; CHANG; LEE,<br>2018        |                               | x                                          |                                   |                          |                           | X            |

| SINGH et al., 2018              | X                             |                                            |                                   | X                        |                           |              |

| ENSAN et al. 2018               |                               | X                                          |                                   |                          |                           | X            |

| PAHUJAA et al.,<br>2017         | X                             |                                            |                                   | х                        |                           | х            |

| LIMACHIA et al.,<br>2017        | X                             |                                            |                                   | x                        |                           |              |

| PENG et al., 2017               | X                             |                                            |                                   |                          |                           | X            |

| ANJU et al., 2017               |                               | X                                          | X                                 |                          |                           | X            |

| Este trabalho                   |                               |                                            |                                   | х                        | х                         | х            |

#### 4 METODOLOGIA

O objetivo deste trabalho é avaliar os impactos da variabilidade de processo, tensão e temperatura (PVT) e envelhecimento por BTI em células SRAM e identificar células mais robustas ou que proponham soluções para operar nas condições avaliadas. A avaliação considera o desempenho a partir dos tempos de escrita e leitura, robustez através das margens de ruído estático, potência total considerando os estados de *hold*, escrita e leitura e potência estática em circuitos de alto desempenho (HP) e baixo consumo (LP) utilizando a tecnologia preditiva PTM (ZHAO; CAO, 2006) de 45nm, 32nm e 16nm. Para atingir este objetivo, foi utilizada a seguinte metodologia:

- 1) Revisão conceitual e do estado da arte;

- 2) Descrição, validação e caracterização elétrica da célula 6T;

- Avaliação dos efeitos de variabilidade, radiação e envelhecimento ao longo da evolução tecnológica na célula 6T;

- 4) Descrição, validação e caracterização elétrica da célula 8T;

- 5) Avaliação da célula 8T e comparação com a 6T;

- 6) Descrição, validação e caracterização da célula 9T;

- 7) Avaliação desta quanto aos efeitos e comparação com a 6T e 8T;

O passo inicial deste projeto foi a revisão conceitual sobre o funcionamento de células SRAM e sobre os parâmetros de caracterização do funcionamento destas células. Esta revisão reforçou como principais parâmetros de caracterização das células SRAM a análise dos seus tempos de escrita e leitura, caracterizando como atraso da célula o pior caso; a análise da estabilidade da célula através das margens de ruído e a análise do consumo total e estático de energia. Para a análise das margens de ruído, foram desenvolvidos procedimentos automatizados que extraem as margens de ruído das células. Também como passo inicial, foi feito um levantamento dos trabalhos atuais relacionados ao projeto de células SRAM, incluindo trabalhos que apresentam propostas de novas células, trabalhos que avaliam determinadas características e efeitos e trabalhos que adotam novas tecnologias.

Inicialmente foi escolhida a célula 6T para ser descrita, validada e realizada a caracterização elétrica. Neste passo foi definida a sequência de operações a ser realizada para caracterização de todas as próximas células SRAM a serem avaliadas neste trabalho. O terceiro passo foi avaliar os efeitos dos três principais desafios para projeto em tecnologia nanométricas,

variabilidade, envelhecimento e falhas por radiação, ao longo de diferentes nodos tecnológicos. Para isso, foram utilizados modelos preditivos disponibilizados pela PTM (ZHAO; CAO, 2006) de tecnologias de 45nm, 32nm, 16nm *bulk* CMOS nos modelos *high performance* e *low power* e as tecnologias de 16nm e 7nm FinFET nos modelos *high performance* e *LSTP* (ALMEIDA et al., 2018). Este primeiro experimento tem por objetivo principal traçar um panorama do impacto destes três parâmetros considerando a evolução tecnológica. Destes experimentos, os resultados indicam que a variabilidade e o envelhecimento são os principais desafios para o projeto de células SRAM em tecnologia de 16nm bulk CMOS.

Todos os experimentos consideram uma coluna com 128 células de memória e os circuitos auxiliares quando necessários, tais como: circuito de escrita, circuito de pré-carga e circuito amplificador de sinais. Das 128 células que compõem a estrutura, apenas 1 é usada na avaliação e comparação. As demais 127 células restantes ficam em *hold*, das quais 63 armazenam o valor '0' e as 64 células restantes armazenam o valor '1'. Estas 127 células são importantes para simular a capacitância das *bitlines* e a interação da corrente estática entre os nodos que armazenam o valor '0' e as *bitlines*.

Os passos 4 a 6 deste trabalho definem a visão geral da metodologia adotada para possibilitar a comparação entre diferentes células quanto aos efeitos de variabilidade PVT e envelhecimento. Todos os passos consideram a célula 6T como célula de referência por ser a mais amplamente adotada na indústria. Por isso, este trabalho inicia com a descrição, caracterização e avaliação da célula 6T. Na sequência, para validar a metodologia proposta quanto a sua utilização para comparação com outras células, foi escolhida a célula 8T para ser descrita, caracterizada, avaliada e comparada com a célula 6. Esta célula foi escolhida por estar presente em vários trabalhos atuais e por ser uma alternativa proposta para aumentar a robustez das margens de ruído de células SRAM.

O passo seguinte foi escolher uma nova célula para fins de comparação. A célula 9T foi escolhida por ser uma adaptação da 8T e por ser uma célula que propõe maior resistência aos efeitos da variabilidade PVT (KIM; LEE; DO, 2018) sem necessitar de dez ou mais transistores como outras propostas encontradas. Os próximos passos deste trabalho foram analisar os resultados das três propostas de célula e verificar quais os pontos positivos e negativos de cada proposta, sob os aspectos de desempenho, robustez, dissipação de potência e consumo estático.

# 4.1 Metodologia de avaliação dos efeitos na tecnologia de 16nm

Para a comparação entre as células de memória SRAM escolhidas, foi considerado o projeto nas tecnologias preditivas *bulk* CMOS PTM de 16nm de alto desempenho (HP) e *low power* (LP) (ZHAO; CAO, 2006). Os circuitos de alto desempenho foram projetados com a tensão de alimentação igual a 0,7V operando a uma frequência de 1GHz, enquanto os circuitos *low power* utilizaram tensão de alimentação igual a 0,3V e frequência de 1KHz. As simulações elétricas foram realizadas usando o simulador NGSpice (NGSPICE, 2018).

Todas as três células foram descritas e validadas logicamente. São observadas as características elétricas de cada célula, considerando os atrasos, as margens de ruído, o consumo total e consumo estático. Após, são feitos os experimentos de avaliação dos efeitos de variabilidade e envelhecimento circuitos de alto desempenho e em circuitos *near-threshold*, como ilustrado no fluxograma da Figura 4.1.

Simulações: Processo HP: 0,7V @1GHz LP: 0,3V @1KHz Análise de Tensão variabilidade PVT Temperatura ı Validação elétrica e análise das células 6T, ı 8T e 9T em condição ı nominal Análise de Bias Temperature **Envelhecimento** Instability (BTI) Avaliado: Tempos de escrita e leitura Potência dinâmica e corrente estática Margens de ruído estático

Figura 4.1 Fluxograma da metodologia de análise das células 6T, 8T e 9T

Fonte: Adaptado de ALMEIDA; BUTZEN; MEINHARDT, 2018b.

#### 4.1.1 Características de implementação das células 6T, 8T e 9T

Inicialmente, este trabalho explora o projeto da célula 6T, adotando a célula 8T para fins de comparação. Estas células são mostradas na Figura 4.2. As células foram dimensionadas para manter uma boa relação entre área, desempenho e estabilidade. A Tabela 4.1 mostra o dimensionamento dos transistores conforme identificados na Figura 4.2 (a). A célula 6T possui os transistores M1 e M2 com maior dimensionamento (maior W), para melhorar sua

estabilidade de leitura. A célula 8T, conforme a Figura 4.2 (b), foi dimensionada para melhorar o desempenho de leitura, porém esta célula não depende de um amplificador de sinais para realizar a leitura por possuir uma *bitline* exclusiva para a leitura (RBL).

Figura 4.2 Células 6T, 8T e 9T

Fonte: (a) PAVLOV; SACHDEV, 2009. (b) CHANG et al., 2005. (c) KIM; LEE; DO, 2018.

| Célula | M1-M2 M3-M4 (pull-down) (pull-up) |      | M5-M6<br>(trans.<br>passagem) | M7-M8<br>(leitura 8T e<br>9T) | M9<br>(leitura 9T) |

|--------|-----------------------------------|------|-------------------------------|-------------------------------|--------------------|

| 6T     | 64nm                              | 32nm | 32nm                          | -                             | -                  |

| 8T     | 32nm                              | 32nm | 32nm                          | 64nm                          | -                  |

| 9T     | 32nm                              | 32nm | 32nm                          | 64nm                          | 64nm               |

Tabela 4.1 Dimensionamento das células SRAM

## 4.1.2 Caracterização dos atrasos

Para a caracterização de uma célula de memória, é importante observar os tempos de escrita e de leitura para cada um dos valores, zero e um, sendo que o pior caso destes caracteriza o atraso da célula. O maior tempo obtido limita a frequência máxima de operação de uma memória SRAM. Neste trabalho, a obtenção de ambos os se faz necessário para verificar os efeitos da variabilidade e do envelhecimento em cada um deles. A variabilidade e o envelhecimento podem modificar os tempos de escrita e leitura obtidos, de forma que em determinadas condições pode ocorrer a inversão de qual tempo é o fator limitante de operação.

O tempo de escrita de uma célula de memória SRAM é o tempo necessário para que o nodo Q leva para adquirir um novo valor lógico, caso o valor anterior seja diferente do que será escrito. Este tempo é calculado entre a ativação de 50% da wordline WL da célula desejada e 50% da transição do nodo Q da célula. O tempo de leitura é definido entre a ativação de 50% da wordline WL da célula desejada e a descarga de 10% da tensão da bitline conectada ao nodo Q ou Qb que armazena o valor lógico '0' (AGAL et al., 2014). A obtenção dos atrasos é realizada durante a validação lógica, que consiste na seguinte sequência: Armazenar '0' em Q,

hold, ler '0' de Q, hold, armazenar '1' em Q, hold, ler '0' de Q. Dessa forma é possível analisar os três estados da célula e verificar se ela está totalmente operacional. Durante essa simulação é possível obter o consumo total da célula de memória. Um exemplo de arquivo de simulação para caracterização de atrasos é apresentado no Anexo I.

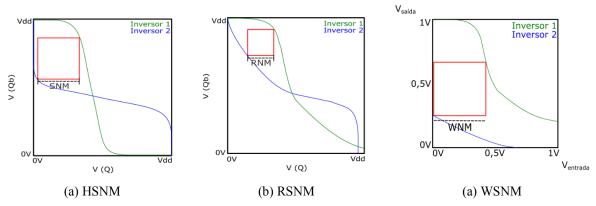

#### 4.1.3 Caracterização das margens de ruído

A integridade dos dados em SRAMs é fundamental para o funcionamento de um circuito digital. Uma métrica de robustez que pode ser usada em células de memória são as margens de ruído estático. Células mais robustas apresentam maiores valores de margem de ruído, ou seja, suportam maior quantidade de ruído sem a perda de dados. Neste trabalho são analisadas três margens de ruído: HSNM (*Hold Static Noise Margim*), RSNM (*Read Static Noise Margin*) e WSNM (*Write Static Noise Margin*). A HSNM é obtida na análise do estado de *hold*, a RSNM é obtida durante a leitura e a WSNM é obtida durante o estado de escrita. Estas margens representam o quanto de ruído uma célula suporta em seus nodos *Q* e *Qb* durante cada estado de operação sem que haja a perda do valor armazenado.

As margens de ruído são obtidas através de simulações DC que reproduzem cada estado de operação de uma célula (*hold*, leitura e escrita) sob a ação de ruído. Para reproduzir o ruído é inserida uma fonte de tensão nos nodos Q e Qb (SEEVINCK; LIST; LOHSTROH, 1987). A A tensão que simula o ruído varia de 0V até a tensão de operação de cada modelo e condição (tensão nominal ou *near-threshold*), fazendo com que em dado momento os inversores mudem o valor lógico armazenado nos nodos Q e Qb. O comportamento dos inversores gera as curvas de transferência de tensão mostradas na Figura 4.4, na qual cada eixo representa a tensão em um dos nodos Q ou Qb. A margem de ruído é definida como o lado do maior quadrado encontrado entre as curvas (SEEVINCK; LIST; LOHSTROH, 1987).

Figura 4.3 ilustra os circuitos utilizados para obter as margens de ruído HSNM (a), RSNM (b) e WSNM (c). Ao inserir um ruído na entrada dos inversores, deve ser observada a

curva de transferência de tensão da saída. Para a escrita, como cada bitline possui um valor diferente, é necessário verificar ambas as condições.

A tensão que simula o ruído varia de 0V até a tensão de operação de cada modelo e condição (tensão nominal ou *near-threshold*), fazendo com que em dado momento os inversores mudem o valor lógico armazenado nos nodos Q e Qb. O comportamento dos inversores gera as curvas de transferência de tensão mostradas na Figura 4.4, na qual cada eixo representa a tensão em um dos nodos Q ou Qb. A margem de ruído é definida como o lado do maior quadrado encontrado entre as curvas (SEEVINCK; LIST; LOHSTROH, 1987).

Figura 4.3 Circuitos para a obtenção das margens HSNM (a), RSNM (b) e WSNM (c)

Fonte: ALMEIDA; BUTZEN; MEINHARDT, 2016.

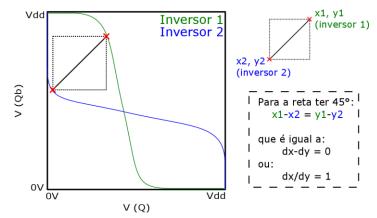

As curvas de transferência de tensão são obtidas através de simulação elétrica, porém para a extração das margens de ruído foi necessário criar um programa para a obtenção dos valores desejados. O programa recebe a especificação do tipo de análise (HSNM, RSNM ou WSNM) e um arquivo com os pontos que representam as curvas. Através de busca exaustiva, são procurados os pontos das curvas que ficam a  $45^{\circ}$  entre si. Há um quadrado se os pontos estão a  $45^{\circ}$  entre si e a diferença de tensão em cada eixo ( $V_Q$  e  $V_{Qb}$ ) seja igual, como ilustrado na Figura 4.5. Como pode haver muitos quadrados, é necessário armazenar apenas o maior encontrado. O programa desenvolvido para encontrar os quadrados e calcular as margens de ruído é mostrado no Anexo II.

Figura 4.4 Curvas de transferência de tensão no estado de *hold* (a), leitura (b) e escrita (c)

Fonte: ALMEIDA; BUTZEN; MEINHARDT, 2016.

Figura 4.5 – Método para encontrar quadrados entre as curvas

Fonte: ALMEIDA; BUTZEN; MEINHARDT, 2016.

### 4.1.4 Caracterização de potência

A energia consumida é obtida de uma fonte de tensão exclusiva para a célula SRAM verificada, mantendo o restante do circuito alimentado por uma segunda fonte de tensão. Ambas as fontes possuem a mesma tensão. O valor de energia é dado pela integral da corrente elétrica durante determinado intervalo de tempo (período). A energia é obtida considerando o período total de simulação para caracterização dos atrasos das células de memória, ou seja, se referem ao consumo total.

Quando é necessário comparar circuitos que não possuem o mesmo período de simulação, pode ser utilizada a potência. A potência é dada pela Equação 4.1, sendo que a

energia é fornecida pelo NGSpice, enquanto que o tempo e a tensão são definidos na simulação realizada.

$$P = \frac{\int_{t0}^{t} idt}{t} * Vdd$$

Equação 4.1

Outro aspecto observado é a corrente estática de cada célula de memória. Esta corrente é obtida a partir de uma simulação DC considerando a célula de memória em estado de *hold*. Esta corrente é obtida exclusivamente da fonte que alimenta a célula.

#### 4.1.5 Experimentos para avaliação de variabilidade PVT

Para simular os impactos da variabilidade de processo, foi utilizada uma distribuição gaussiana de  $3\sigma$  com a variação de 10% na tensão de limiar que reproduz a variação geométrica no dispositivo. Para cada tipo de análise foram executadas 2000 simulações de Monte Carlo (ALIOTO, 2015). Para alterar a tensão de limiar dos modelos utilizados, é necessário modificar os parâmetros vthn0 e vthp0 do modelo PTM utilizado, estes parâmetros se referem à tensão de threshold base, que é utilizada para a obtenção da tensão de threshold após as condições de operação e dimensionamento do circuito estarem definidas. Para isso, é necessário inserir duas variáveis vthn e vthp que variam entre -10% e +10% de uma distribuição gaussiana de  $3\sigma$  em relação ao valor nominal.

O NGSpice não disponibiliza a função Monte Carlo, para isso foi criado um programa na linguagem C que realiza 2000 chamadas do executável NGSPICE com a netlist da simulação como parâmetro. Um exemplo da netlist que possui a função parar variar a tensão de limiar encontra-se no Anexo I e um exemplo do programa para rodar 2000 vezes esta netlist é apresentado no Anexo II. Destas 2000 simulações, cada uma assume um valor aleatório respeitando os parâmetros inseridos na distribuição gaussiana. Para cada célula, o programa deve ser executado três vezes: caracterização de atrasos e de energia; caracterização das margens de ruído e caracterização do consumo estático. Todos os resultados são analisados, observando-se os valores mínimos, máximos, média (μ), desvio padrão (σ) e coeficiente de variação (σ/μ) de cada caracterização.

Para analisar a variabilidade de tensão é realizada através da mudança da tensão de alimentação para -10% e +10% do valor nominal. Este tipo de variabilidade afeta os aspectos de desempenho e potência de forma inversamente proporcional. Ao aumentar a tensão há o ganho de desempenho e robustez, mas aumenta também a potência dinâmica e estática. Ao

reduzir a tensão há a redução de potência estática e dinâmica e consequentemente a redução do desempenho e robustez.

A variabilidade de temperatura é verificada através da mudança da variável de temperatura no ambiente de simulação. Neste trabalho foi observada uma variação de entre 0°C e 125°C com o passo de 25°C. Através da variação observada nestas temperaturas é possível estimar temperaturas intermediárias e até mesmo superiores a 125° ou inferiores a 0°.

#### 4.1.6 Experimentos para avaliação de efeitos de envelhecimento

Os efeitos de envelhecimento por NBTI e PBTI foram modelados como uma degradação de 50mV na tensão de limiar dos transistores no decorrer de 5 anos de uso contínuo e o modelo apresentado em (BUTZEN et al., 2013). A probabilidade de estresse dos transistores que compõem o laço de inversores foi de 50%. Como cada célula de memória passa majoritariamente em estado de *hold*, foi considerada a chance de 0,01% do uso do transistor de passagem. Outro fator que contribui para o baixo uso dos transistores de passagem é devido a chance de a célula ser acessada entre as 128 células que compartilham a mesma coluna. Para os circuitos auxiliares foi considerado o uso em 98% do tempo da pré-carga, e 1% para os circuitos de escrita e amplificador de sinais.

Estes valores são aplicados na Equação 4.2, proposta por (WANG et al., 2007). Considera-se  $\Delta Vth$  a variação máxima da tensão de limiar, b uma constante da tecnologia utilizada,  $\alpha$  é a probabilidade de uso do transistor no decorrer do tempo total, n é uma constante exponencial de tempo igual a 0,16 e t é o tempo total.

$$\Delta Vth = b * \alpha^n * t^n$$

Equação (4.2)

#### 5 RESULTADOS

Circuitos produzidos em tecnologias nanométricas se mostram muito sensíveis a variações PVT e envelhecimento por BTI. Estes efeitos são ainda mais graves em circuitos *low power*. Dessa forma, a comunidade científica vem estudando estes efeitos em diversos tipos de circuitos combinacionais e sequenciais. Em memórias SRAM estes efeitos podem inutilizar blocos inteiros de células devido a uma única célula que apresente mau funcionamento. Diante da alta densidade de células em relação a área que elas ocupam e a necessidade de reduzi-las cada vez mais as torna mais sensível a variações.

Os resultados são apresentados iniciando pelo experimento inicial de avaliação do impacto da variabilidade, radiação e envelhecimento ao longo da evolução tecnológica. A segunda parte dos resultados compara os efeitos dos principais desafios nas células 6T, 8T e 9T.

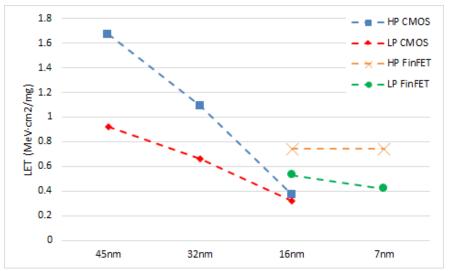

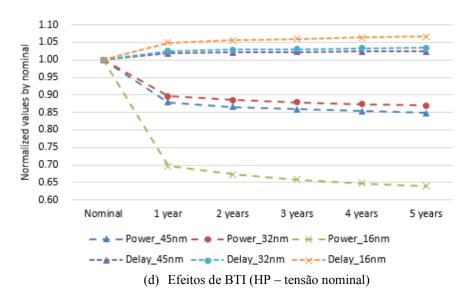

#### 5.1 Impacto da variabilidade, radiação e envelhecimento em tecnologias nanométricas